# **High Performance Low Cost Off-line PWM Power Switch**

#### **FEATURES**

- Integrated with 700V Power MOSFET and HV Startup Circuit

- Multi-Mode Control with Audio Noise Free Operation

- Supports Flyback, Buck and Buck-Boost Topologies

- Support Ultra-low Input Voltage (>20V)

- Less than 100mW Standby Power

- Up to 40kHz Maximum Frequency

- Good Line and Load Regulation

- Built-in Soft Start

- Build in Protections:

- Over Load Protection (OLP)

- Cycle-by-Cycle Current Limiting (OCP)

- Abnormal Over Current Portection (AOCP)

- Output OVP

- On-chip OTP

- Available with SOP-8 Package

#### **APPLICATIONS**

Small Home Appliances

#### GENERAL DESCRIPTION

KP3116 is a high performance Switch Mode Power Supply Switcher for low power off-line application with minimum components in typical buck solution. This IC has built-in high break down voltage MOSFET to withstand high surge input.

Unlike conventional PWM control, there's no fixed internal clock in KP3116 to trigger the GATE driver, the switching frequency is changed according to the load condition. The multi-mode PWM control is integrated to simplify circuit design and achieve good line and load regulation without audio noise generated. The peak current limit changes according to the real load condition for low standby power in no load.

KP3116 integrates functions and protections of Under Voltage Lockout (UVLO), Cycle-by-cycle Current Limiting (OCP), Abnormal Over Current Portection (AOCP), Output OVP, On-chip Thermal Shutdown, Over Load Protection (OLP) with Auto Recovery Mode Protection, etc.

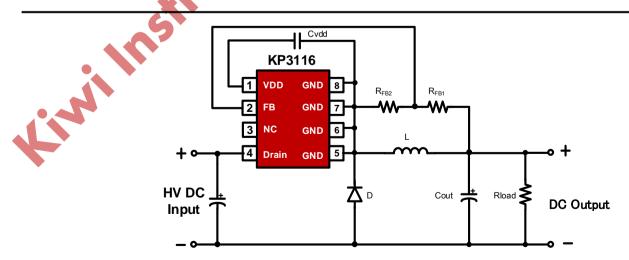

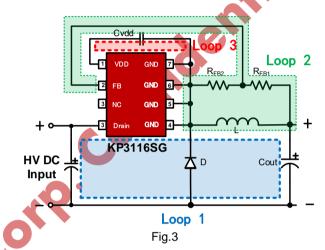

#### TYPICAL APPLICATION CIRCUIT

## **Pin Configuration**

## **Marking Information**

XXXXXX: Wafer Lot Code Y: Year Code WW: Week Code, 01-52 ZZ: Serial Number, 01-99 or A0-ZZ 8 7 6 5 **KP3116SG XXXXXX** 0 **YWWZZ**

2 3

## **Typical Output Power Table**

| Product | Package | Rdson | Output<br>Voltage | Output Current @85-265Vac,<br>BUCK,85°C |

|---------|---------|-------|-------------------|-----------------------------------------|

| KP3116  | SOP-8   | 14Ω   | >2V               | lo<350mA                                |

#### Note:

- Default for Buck Converter Application

- The practical output power is determined by the output voltage and thermal condition

## **Pin Description**

| Pin Number | Pin Name | I/O | Description                                                                                                                                     |

|------------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VDD      | Р   | The power supply and the output voltage feedback pin. For the normal operation, a capacitor with $1\mu F$ is recommended to connect to this pin |

| 2          | FB       | I   | Feedback Input                                                                                                                                  |

| 3          | NC       | /   | No Connection                                                                                                                                   |

| 4          | DRAIN    | Р   | The Power MOSFET Drain                                                                                                                          |

| 5,6,7,8    | GND      | Р   | The Ground Reference for the IC                                                                                                                 |

## **Ordering Information**

| Part Number | Description                               |  |  |

|-------------|-------------------------------------------|--|--|

| KP3116SGA   | SOP-8, Halogen free in T&R, 4000 Pcs/Reel |  |  |

Note: Suffix "A" - Tape&Reel

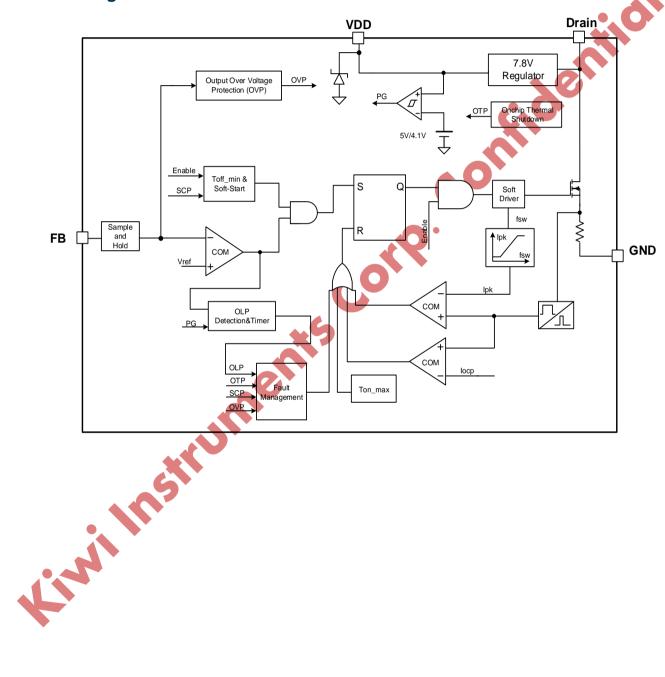

## **Block Diagram**

# **Absolute Maximum Ratings (Note 1)**

| Parameter                                                | Value       | Unit |

|----------------------------------------------------------|-------------|------|

| Drain Pin Voltage Range                                  | -0.3 to 700 | V    |

| VDD Pin Voltage Range                                    | -0.3 to 9   | V    |

| VDD Pin Clamp Current                                    | 10          | mA   |

| FB Voltage Range                                         | -0.3 to 9   | V    |

| Package Thermal Resistance – Junction to Ambient (SOP-8) | 165         | °C/W |

| Maximum Junction Temperature                             | 150         | °C   |

| Storage Temperature Range                                | -65 to 150  | °C   |

| Lead Temperature (Soldering, 10sec)                      | 260         | °C   |

| ESD Capability, HBM (Human Body Model)                   | 5500        | V    |

| Maximum Internal MOSFET DC Drain Current                 | 0.8         | А    |

| Drain Maximum Pulse Current (Tpulse=100µs)               | 2.4         | А    |

# **Recommended Operation Conditions**

| Parameter                      | Value      | Unit |

|--------------------------------|------------|------|

| Operating Junction Temperature | -40 to 125 | °C   |

| Operation Switching Frequency  | 30 to 40   | kHz  |

# Electrical Characteristics (Ta = 25°C, If Not Otherwise Noted)

| Symbol                  | Parameter                                | Test Conditions      | Min. | Тур. | Max. | Unit |  |

|-------------------------|------------------------------------------|----------------------|------|------|------|------|--|

| High Voltag             | High Voltage Startup Section (Drain Pin) |                      |      |      |      |      |  |

| I <sub>HV1</sub>        | HV Charging Current1                     | Drain=40V, VDD=0V    | 0.29 | 0.55 | 0.81 | mA   |  |

| I <sub>HV2</sub>        | HV Charging Current2                     | Drain=40V, VDD=4V    |      | 2.8  |      | mA   |  |

| I <sub>HV_leakage</sub> | HV Leakage Current                       | Drain=700V, VDD=8.5V |      |      | 50   | μΑ   |  |

| V <sub>BR</sub>         | HV MOSFET Breakdown<br>Voltage           |                      | 700  |      |      | V    |  |

| Rdson                   | Static Drain-Source On Resistance        |                      |      | 14   |      | Ω    |  |

| Supply Volt             | Supply Voltage Section (VDD Pin)         |                      |      |      |      |      |  |

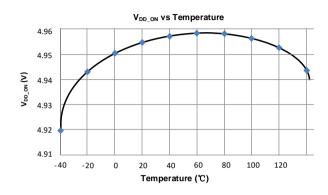

| V <sub>DD_ON</sub>      | VDD Under Voltage Lockout Exit           |                      | 4.5  | 5    | 5.7  | V    |  |

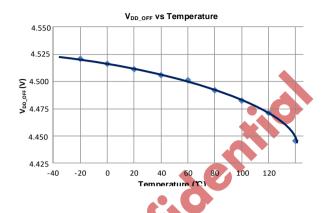

| V <sub>DD_OFF</sub>     | VDD Under Voltage Lockout Enter          |                      | 4    | 4.5  | 5    | V    |  |

## High Performance Low Cost Off-line PWM Power Switch

| V <sub>DD_REG</sub>        | VDD Regular Operating Voltage                               |                         | 7    | 7.5  | 8    | V  |

|----------------------------|-------------------------------------------------------------|-------------------------|------|------|------|----|

| VCLAMP                     | VDD Clamp Voltage                                           | I <sub>CLAMP=</sub> 2mA |      | 9    |      | V  |

| IVDD_Op                    | Operation Current                                           | Fsw=30kHz               |      | 280  |      | μΑ |

| I <sub>VDD_Q</sub>         | Quiescent Current                                           | No Switching            | 90   | 160  | 210  | μΑ |

| Feedback Se                | ection (FB Pin)                                             |                         |      |      |      |    |

| V <sub>FB_REF</sub>        | Internal Error Amplifier (EA)<br>Reference Input            |                         | 1.75 | 1.78 | 1.82 | V  |

| V <sub>FB_OVP</sub>        | Output Over Voltage<br>Protection (Output OVP)<br>Threshold |                         |      | 2.6  |      | V  |

| N <sub>FB_OVP</sub>        | OVP Debounce Cycle                                          |                         | C    | 7    |      |    |

| V <sub>FB_OLP</sub>        | Output Over Load Protection (Output OLP) Threshold          |                         |      | 1.66 |      | V  |

| T <sub>D_OLP</sub>         | Over Loading Debounce Time                                  |                         | 9    | 130  |      | ms |

| Current Sen                | se Section                                                  |                         |      |      |      |    |

| T <sub>LEB</sub>           | Leading Edge Blanking Time                                  | 10.                     |      | 380  |      | ns |

| T <sub>D_OCP</sub>         | Over Current Detection and Control Delay                    | 40                      |      | 50   |      | ns |

| Госр                       | Over Current Detection Value                                |                         | 480  | 500  | 520  | mA |

| IAOCP /IOCP                | AOCP/OCP Ratio                                              | 9                       |      | 1.33 |      |    |

| Timer Section              | on                                                          |                         |      |      |      |    |

| Toff_min_norm              | Normal Minimum OFF time                                     | Stable state            | 21   | 24   | 27   | μs |

| Toff_max_nom               | Nominal Maximum OFF Time                                    |                         |      | 2.3  |      | ms |

| T <sub>ON_max</sub>        | Maximum ON Time                                             |                         | 17   | 28   | 42   | μs |

| Tss                        | Internal Soft Start Time                                    |                         |      | 3    |      | ms |

| T <sub>Auto_Recovery</sub> | Protection Auto Recovery Debounce Time                      |                         |      | 1.3  |      | S  |

| On-Chip Thermal Shutdown   |                                                             |                         |      |      |      |    |

| T <sub>SD</sub>            | Thermal Shutdown Trigger Point                              | (Note 2)                |      | 155  |      | °C |

|                            |                                                             | -                       |      |      |      |    |

**Note1.** Stresses listed as the above "Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note2. Guaranteed by design.

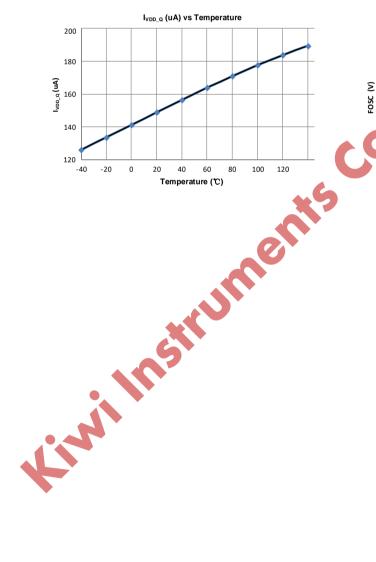

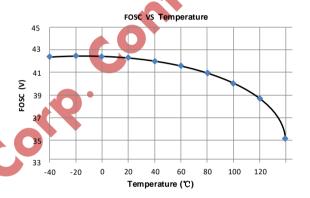

#### **Characterization Plots**

#### **Operation Description**

KP3116 integrates a multi-mode PWM controller with high voltage power MOSFET switch on the IC. It is optimized for off-line non-isolated buck or buck-boost applications in small home appliances and linear regulator replacement. The IC utilizes the multi-mode PWM control to regulate output with high precision and lowest components count.

#### Very Low Operation Current

The standby operating current in KP3116 is as small as 160µA (typical). The small operating current results in higher efficiency and reduces the VCC hold-up capacitance requirement.

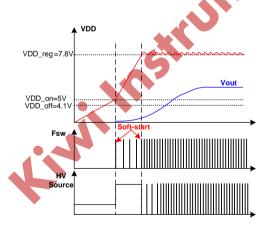

#### High Voltage Start-Up Operation

In KP3116, a 700V high voltage startup cell is integrated. During startup, the internal startup circuit is enabled and a HV current source charges the VDD hold up capacitor Cvdd through Drain pin, as shown in "Block Diagram". When VDD reaches turn-on voltage (5V typical), the IC begins switching and the IC current consumed increased to 0.28mA (typical). The VDD is always charged by the high voltage startup cell in steady state (VDDREG, 7.5V typical).

Fig.1

#### Constant Voltage Control

During the power MOSFET off period, KP3116 samples the FB pin signal which indicates the output voltage, then using the internal Sample & Hold circuit and constant voltage control circuit to guarantee FB pin voltage meet the internal reference V<sub>FB\_REF</sub> (1.78V, typical). So that constant output voltage is achieved.

Below equation approximately determines the output voltage:

$$Vo = 1.78V * \frac{Rup + Rdown}{Rdown} - V_F$$

VF---Freewheeling Diode Voltage. This parameter is offset by the forward current in practical application.

# Current Limit and Leading Edge Blanking

There's a programmable current limit for current sensing voltage, which is changed according to the system switching frequency. When the sampled voltage exceeds the internal threshold, the power MOSFET is turned off for the remainder of that cycle. An internal leading edge blanking circuit is built in. During this blanking period (380ns, typical), the cycle-by-cycle current limiting comparator is disabled and cannot switch off the GATE driver.

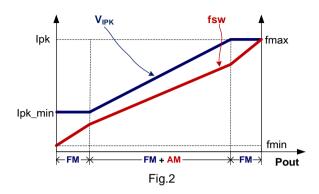

#### Multi-Mode PWM Control

To meet the tight requirement of averaged system efficiency and no load power consumdption, a hybrid of frequency modulation (FM) and amplitude modulation (AM) is adopted in KP3116 which is shown in the Fig 2.

Around the full load, the system operates in FM mode. When normal to light load conditions, the IC operates in FM+AM mode to achieve excellent regulation and high efficiency. When the system is

near zero loading, the IC operates in FM again for standby power reduction.

#### **Soft Start**

KP3116 features an internal 3ms (typical) soft start that slowly increases the switching frequency (Toff reduce from 100µs to 24µs linearly) during startup sequence. Every restart attempt is followed by the soft start activation.

#### **Output Over Voltage Protection (OVP)**

In KP3116, if the sampled FB voltage is larger than 2.6V and lasts for 7 continuous PWM cycles, the IC will enter into Output Over Voltage Protection (Output OVP) mode, in which auto recovery mode will be followed.

#### Over Load Protection (OLP) / Short Load Protection (SLP)

If over load or short load condition occurs, the output and the feedback voltage drop down to be lower than V<sub>FB\_OLP</sub>. If this fault is present for more than 130ms (typical), the protection will be triggered, the IC will experience an auto-restart mode (as mentioned below).

#### **Abnormal Over Current Protection** (AOCP)

When in heavy load or output short condition, the inductor current may be increased too large. To avoid system components damaged, there's a abnormal over current limit (typically 1.33\*OCP). When the current sense voltage is larger than this threshold, the internal power MOSFET is turned off immediately and is to be turned on again after 48µs.

#### On Chip Thermal Shutdown

High Performance Low Cost Off-line PWM Power Switch

KP3116 integrates thermal shutdown function. When the IC junction temperature is higher than 155 °C, IC shuts down and enters into auto-restart mode (as mentioned below).

## **Enhanced Dynamic Response**

In KP3116, the dynamic response performance is optimized to reduce output drop in load transient.

#### **Audio Noise Free Operation**

In KP3116, the optimized combination of frequency modulation and CS peak voltage modulation algorithm can provide audio noise free operation from full loading to zero loading.

#### **Protections with Auto-Restart**

In the event of protections, the IC enters into autorestart and an internal timer begins counting, wherein the power MOSFET is disabled. When 1.3s had been counted, the IC will reset and start up the system again. However, if the fault still exists, the system will experience the above mentioned process.

#### **Soft Totem-Pole Gate Driver**

KP3116 has a soft totem-pole gate driver with optimized EMI performance.

### **Application Information**

#### PCB Layout Guidelines

PCB layout design has a significant impaction on the performance of power supply, which helps KP3116 to improve system reliability, EMC and thermal performance. Follow below guidelines to optimize performance.

- The main power loop (Loop1) should be as small as possible, and the trace should be wide for better efficiency performance.

- 2. Feedback Routing (Loop2): a) Put the feedback loop out of the main power loop, and minimize this loop area as small as possible; b) Do not route FB pin line too long and beneath the IC, or system may not operation normally; c) Put the components of this loop close to IC as much as possible, and far away from the power inductor; d) Place the output feedback point at the positive of the output capacitor, and do not route this line beneath the power inductor or freewheeling diode in case high-frequency noise coupled: e) Make sure signal ground of FB line and IC are connected firstly, then connect to power ingl ground of inductor through a single point.

- 3. Place VDD capacitor close to the IC to ensure the VDD loop (Loop3) is small.

- 4. Additional Notes: a) When  $\pi$  filter circuit is added after the bridge, make sure power inductor far away from the  $\pi$  filter inductor; b) Connect the GND pin of KP3116 to a large cooper area to improve thermal performance if possible.

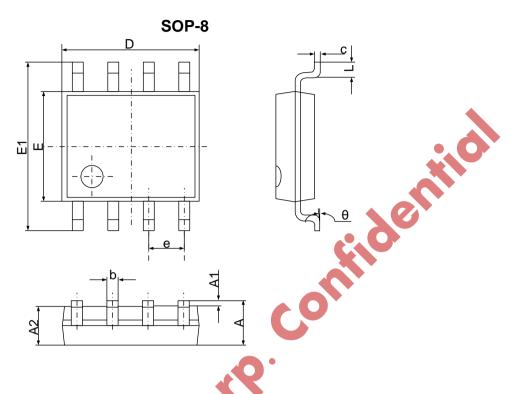

# **Package Dimension**

| Symbol | Dimensions in Millimeters |       | Dimensions  | in Inches |  |

|--------|---------------------------|-------|-------------|-----------|--|

|        | Min.                      | Max.  | Min.        | Max.      |  |

| А      | 1.350                     | 1.750 | 0.053       | 0.069     |  |

| A1     | 0.100                     | 0.250 | 0.004       | 0.010     |  |

| A2     | 1.300                     | 1.500 | 0.051       | 0.059     |  |

| b      | 0.330                     | 0.510 | 0.013       | 0.020     |  |

| С      | 0.170                     | 0.250 | 0.007       | 0.010     |  |

| D      | 4.700                     | 5.100 | 0.185       | 0.201     |  |

| E      | 3.800                     | 4.000 | 0.150       | 0.157     |  |

| E1     | 5.800                     | 6.200 | 0.228       | 0.244     |  |

| е      | 1.270 (BSC)               |       | 0.050 (BSC) |           |  |

| Ł      | 0.400                     | 1.270 | 0.016       | 0.050     |  |

| θ      | 0°                        | 8°    | 0°          | 8°        |  |

#### **Disclaimer**

Kiwi reserves the right to make any change to its product, datasheet or specification without any notice. Users shall obtain the latest information before placing an order. Kiwi herein makes no guarantee or warranty, expressed or implied, including without limitation the warranties of merchantability, fitness for any purpose or non-infringement of third party rights, nor does Kiwi convey any license or permission including without limitation the intellectual property rights of Kiwi or any third party. Users should warrant that third party intellectual property right or other right is not infringed when integrating Kiwi products into any application or in use. Kiwi will not assume any liability arising from any said application or use, and especially disclaim any liability including without limitation any consequential or incidental damage. Without written declaration, Kiwi products are not designed for use in surgical device implant into the body or other life sustain systems. This disclaimer supersedes the disclaimers in previous versions.

a. any to argical devices control of the control of