### Chapter 1 BF7707AMXX MCU general description

#### 1.1. Features

#### Core: ARM Cortex-M0+

- Operating frequency: 48MHz, 32MHz, 24MHz, 12MHz

Clock error: ±1% @-20°C~65°C, 5V; ±3% @-40°C~105°C, 5V

- Single-cycle 32-bit hardware multiplier

#### Memory (FLASH)

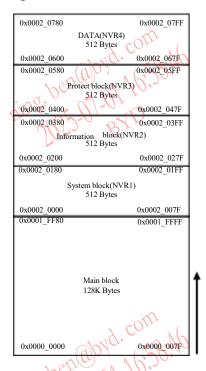

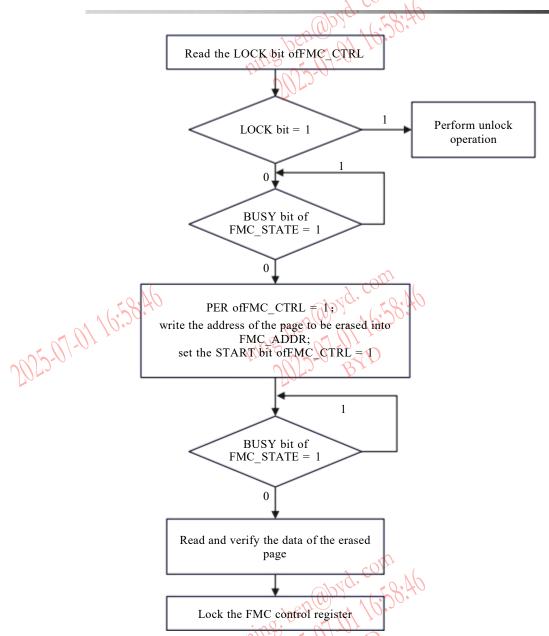

- FLASH: 128K Bytes, support erase and write protection and read protection functions

- DATA: 512 Bytes

- o SRAM: 12K Bytes

#### Clock source, reset and power management

- Internal low-speed RC oscillator: LIRC 32kHz, clock error is ±10% @25°C, 5V; ±25% @-40°C ~105°C, 5V

- o Internal high-speed RC oscillator: RC 1MHz

- External crystal oscillator: XTAL 32768Hz/4MHz/8MHz passive crystal and active crystal(1MHz~48MHz)

- 7 resets, power-down reset voltage (BOR):

2.8V/3.3V/3.7V/4.2V(configured by option byte area)

- o Low voltage detection: 2.7V/3.0V/3.3V/3.6V/3.9V/4.2V/4.5V

#### IC

- o Both support built-in pull-up resistor 12k

- High current sink port (PA0~PA7)

- Support IO function remapping

- 16 external interrupt input channels, all EXTI support any I/O port mapping, support rising edge/ falling edge/ double edge trigger, edge wake up, support interrupt filtering

#### > Communication module

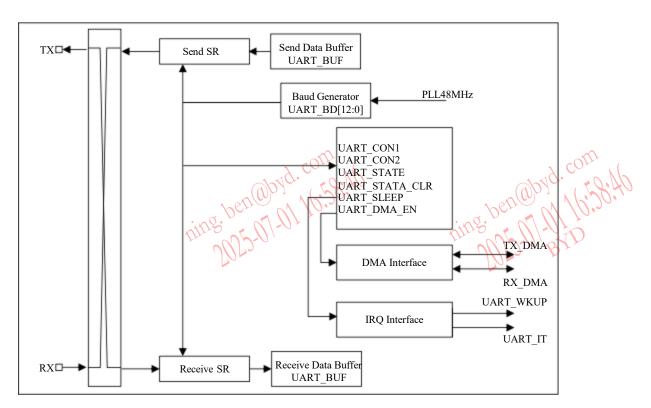

- 5xUART communication module, UARTx supports remapping,

TXD/RXD configuration, receiving idle, transmitter output polarity and receiver input polarity are optional

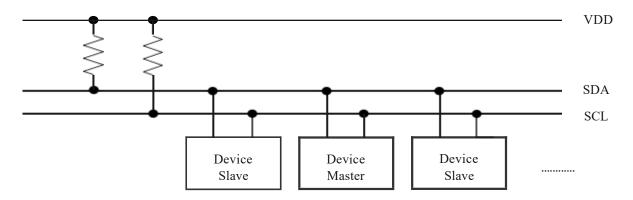

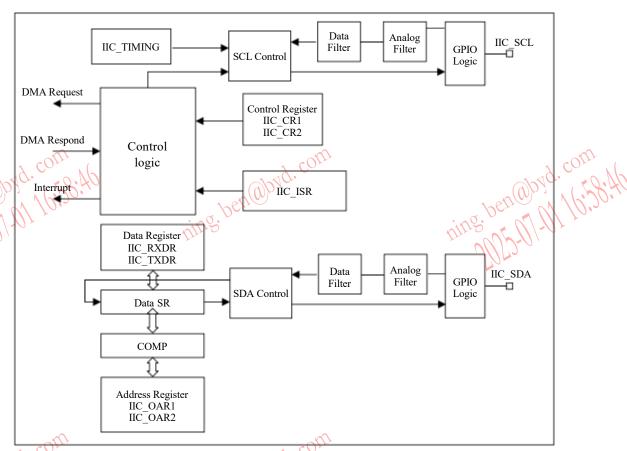

- 1xIIC master-slave communication, both master and slave support 100kHz/400kHz/1MHz

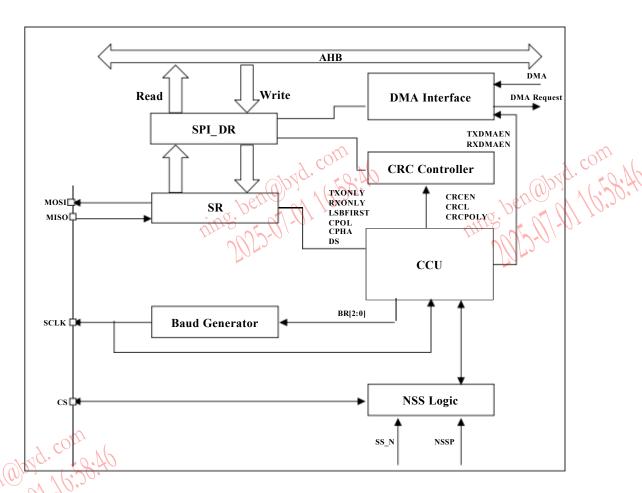

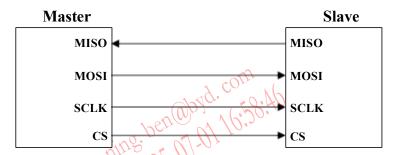

- 2xSPI master-slave communication, the master supports up to 8MHz, the slave supports up to 4MHz, support CRC hardware check

#### ➤ 16-Bit PWM

- o PWM0 supports one output and three mappings

- o PWM1 supports one output and three mappings

- Support timing mode

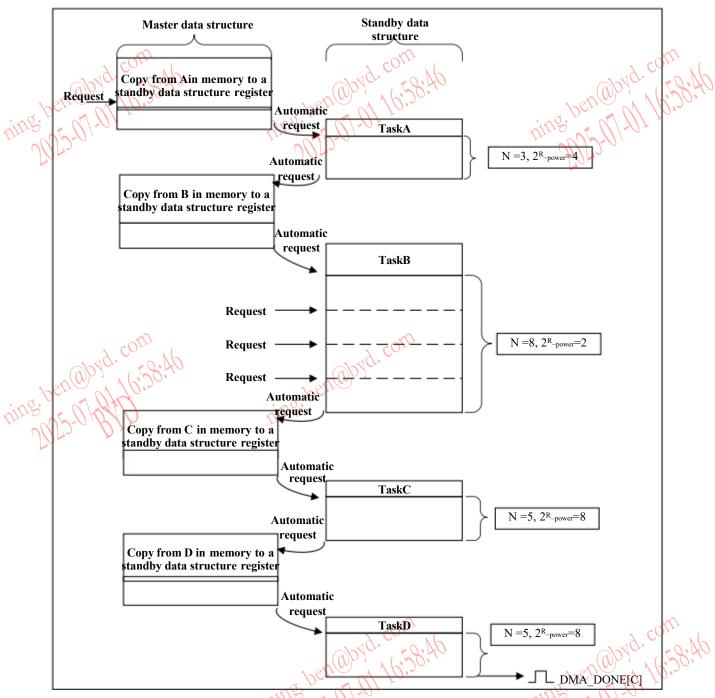

#### DMA

- 3 channels, each channel has a separate interrupt enable and interrupt flag

- Supports transmission between memory and memory, peripherals and memory

- o Two channel priorities can be matched

- o Supports peripherals TIM, ADC, SPI, IIC, and UART

- Operating voltage: 2.6V ~5.5V

- ➤ Operating temperature: -40°C ~105°C

- Enhanced industrial grade, in line with the JESD industrial grade reliability certification standards

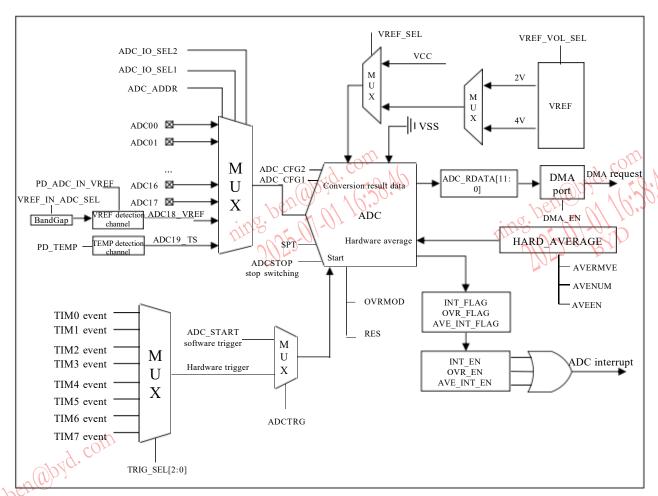

#### High precision 8/12-bit ADC, 1M sps ADC

- o 18 GPIO analog input channels

- 2 internal analog inputs: VREF channel (internal channel reference voltage channel), TS channel (built-in temperature sensor)

- Trigger mode can be software register trigger or hardware event trigger

- o Reference voltage: VCC/2V/4V

- Single conversion (including hardware average) /DMA continuous conversion mode

#### Interrupt

- o 29 interrupt sources

- 4-level interrupt priority can be configured

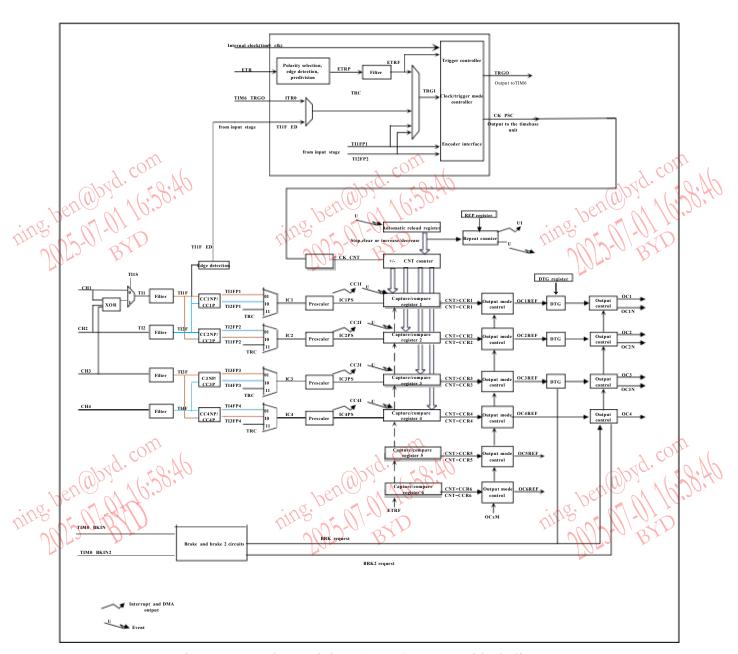

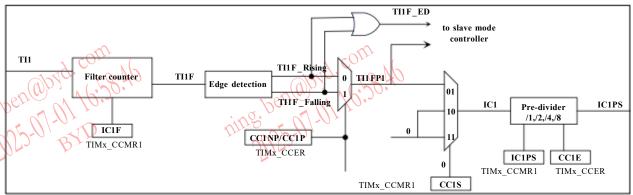

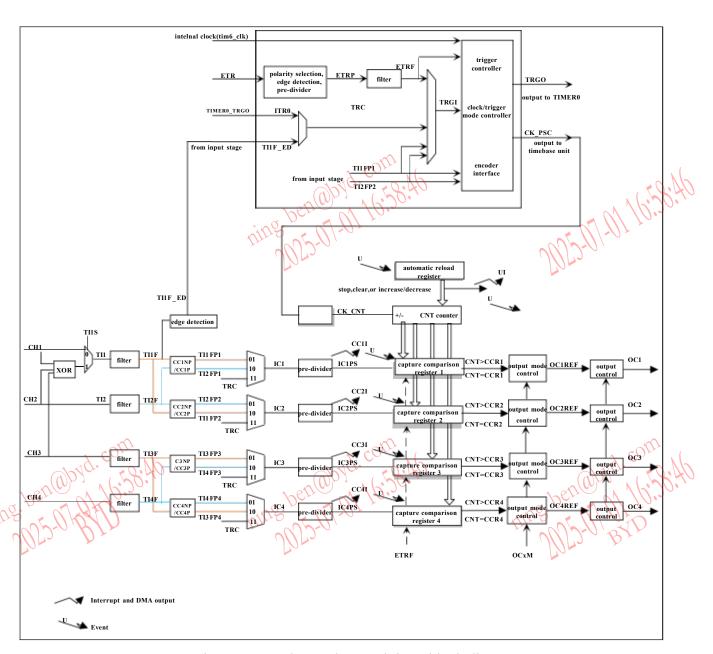

#### Timer

- o 16-bit advanced control timer: 1 (TIM0)

- o 16-bit universal timer: 7 (TIM1/2/3/4/5/6/7)

- TIM0: 6 independent channels, 16 bit increment, decrement, increment/decrement automatic overload counter

- TIM0 supports programmable dead-time complementary output and brake input

- o TIM1/2/3/4/5/7: 1 independent channel, 16-bit increment automatic overload counter

- TIM6: 4 independent channels, 16 bit increment, decrement, increment/decrement automatic overload counter

- TIM0 and TIM6 support incremental encoders and hall sensor circuits

- TIM supports input capture (except for channel 5/6), output comparison, PWM generation, and one-pulse mode output

- Watchdog timer: overflow time ranges from 18ms to 2.304s

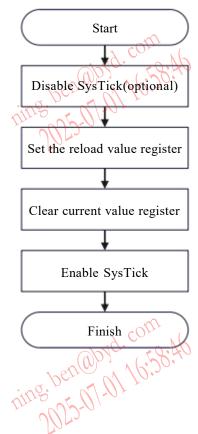

- o SysTick Timer

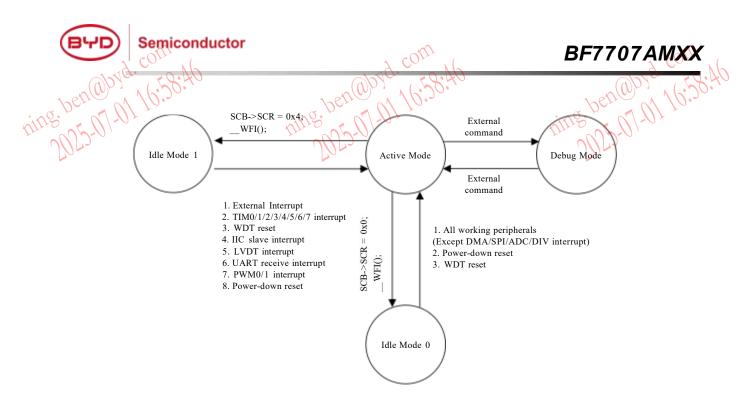

#### Low power management

- $\circ \quad \text{Idle mode 0, power consumption 1.9mA} \underline{@} 5V \ typical$

- o Idle mode 1, power consumption 6. 1μA@5V typical

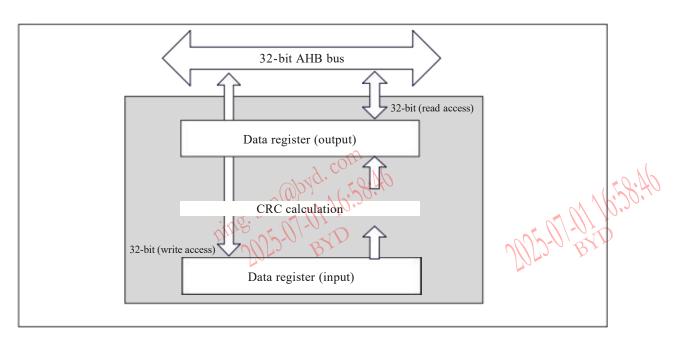

#### Cyclic redundancy check unit

- o CRC8/16/32, used for code check and data check

- hardware divider

- o 32-bit divider (signed and unsigned operations can be selected)

- o 16 clock cycles to complete the operation

- **128-bit chip unique identification code**

- Serial two-wire debugging interface SWD, PGC/PGD programming

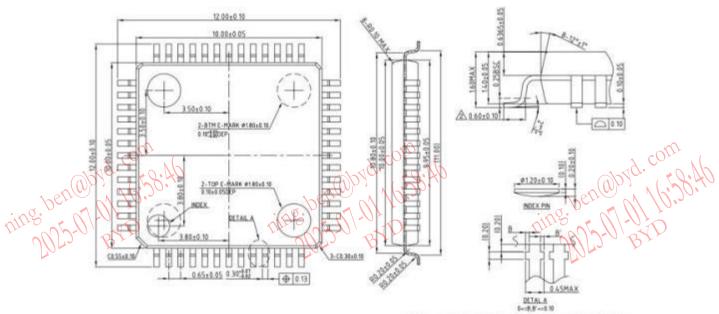

- Package

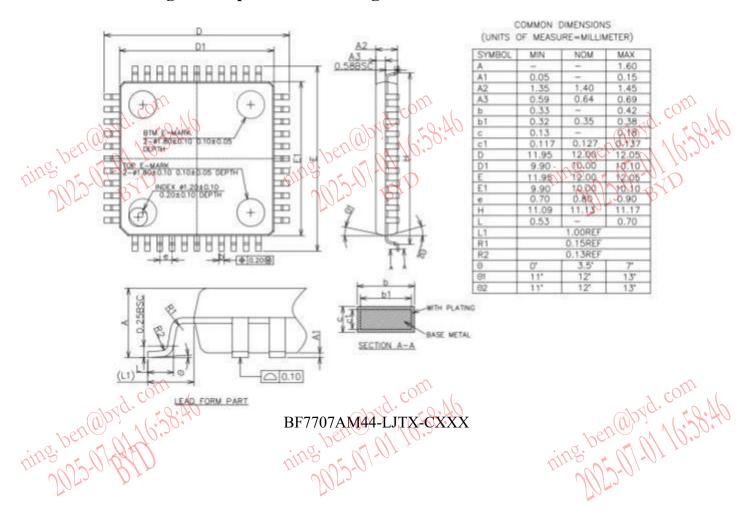

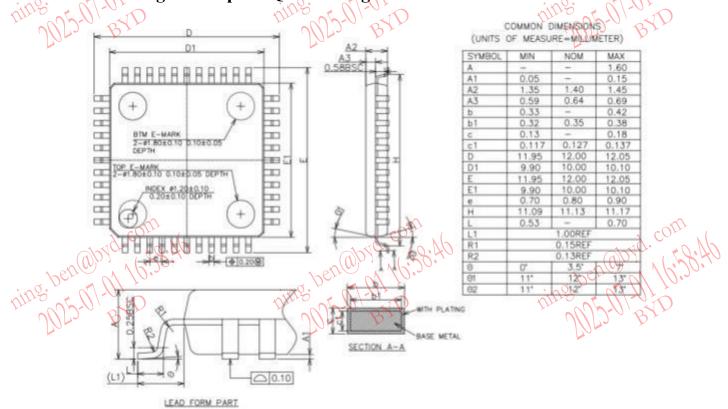

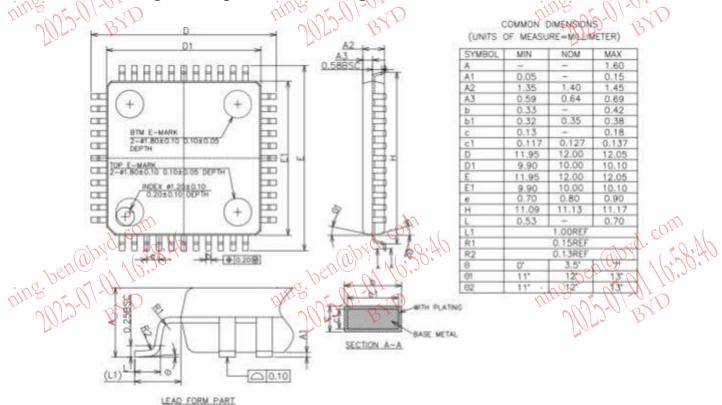

- O LOFP44/LOFP52/LOFP64

Datasheet Page 1 of 449

#### 1.2. Overview

BF7707AMXX is a 32-bit high performance microcontroller based on the ARM Cortex-M0+ core. The Cortex-M0+ core is based on the ARMv6-M architecture and supports the Thumb instruction set.

BF7707AMXX series working voltage is 2.6V~5.5V, working temperature is -40°C~+105°C, products provide a variety of different working modes, in order to cope with the power consumption needs in different situations. BF7707AMXX is embedded with 128KB Flash and 12KB SRAM, with a maximum operating frequency of 48MHz.

The product offers 8 16-bit timers (1 advanced control timer, 7 universal timers). The product provides a variety of standard communication interfaces: 5-channels UART, 1-channel IIC, 2-channels SPI, 8/12 bit high-precision 1M high-speed ADC with optional resolution ratio, and with VCC/ 2V/4V reference ADC voltage function, its integrated temperature sensor can realize real-time monitoring of its own temperature. Powerful DMA data handling function, external interrupt function can be freely mapped to any port.

BF7707AMXX series provides CRC code check and data check of 8/16/32 bits, built-in watchdog timer, low voltage reset circuit, power failure detection circuit and other modules.Low power management of BF7707AMXX series can cope with power consumption requirements in different situations.

Datasheet Page 2 of449

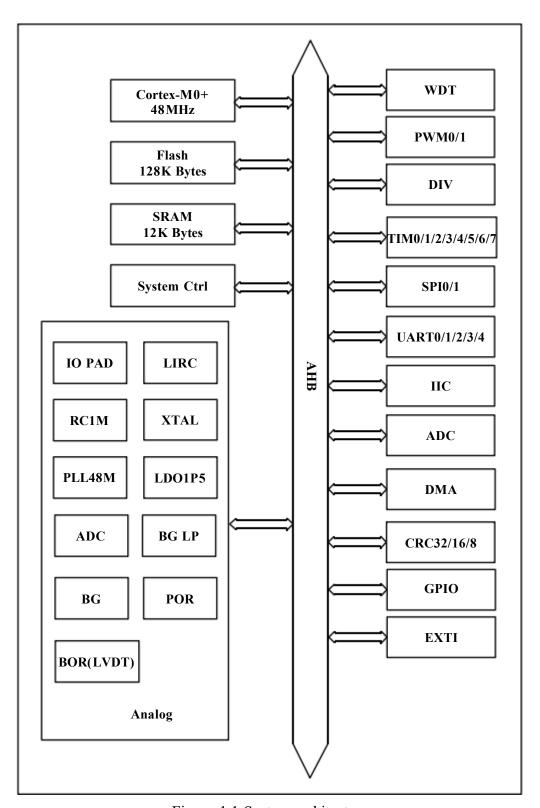

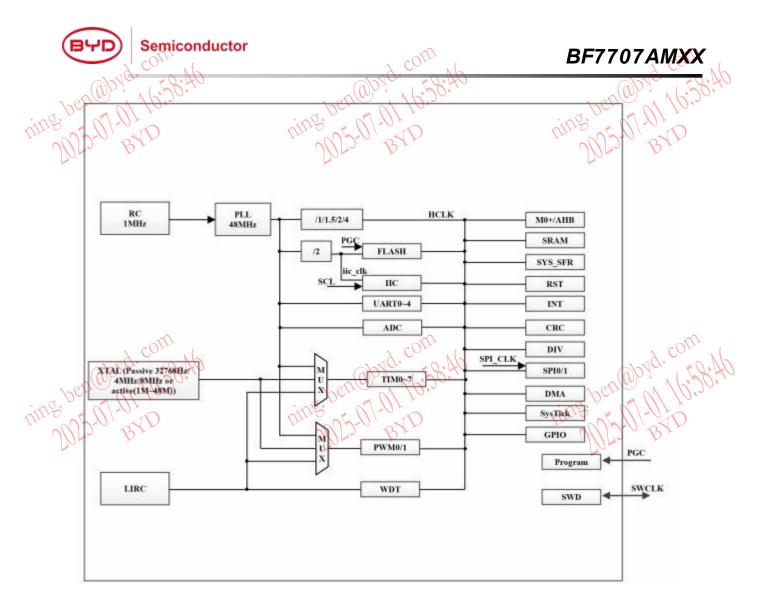

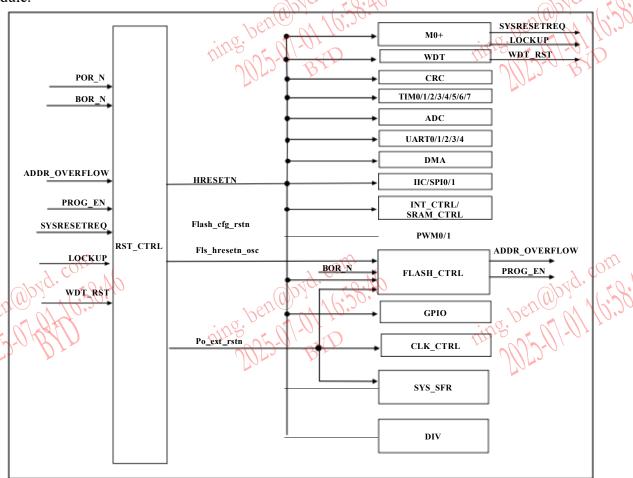

# 1.3. System architecture

Figure 1.1 System architecture

Datasheet Page 3 of449

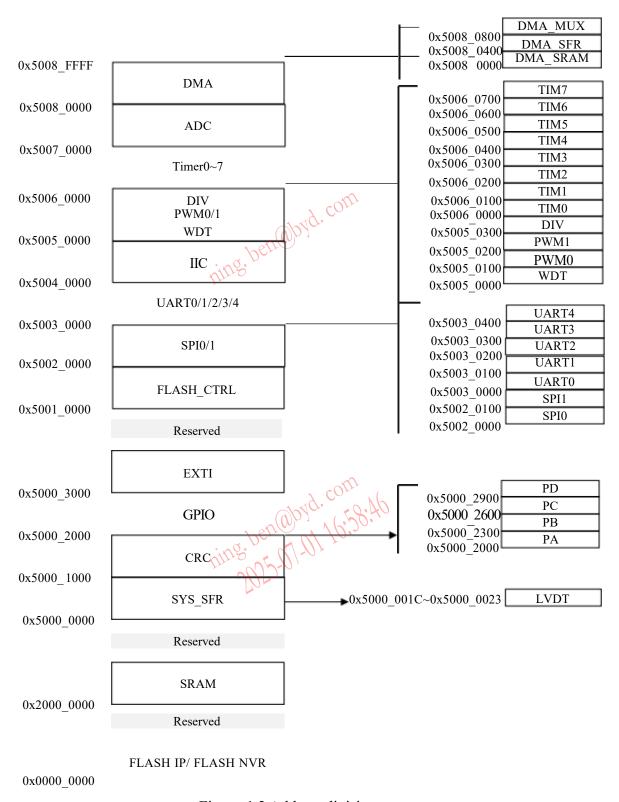

#### 1.4. Memory map

Figure 1.2 Address division map

Datasheet Page 4 of449

| Start address | End address | Size(Bytes) | Module                 |  |

|---------------|-------------|-------------|------------------------|--|

| 0x0000_0000   | 0x0002_07FF | 130K        | FLASH IP 、FLASH NVR    |  |

| 0x2000_0000   | 0x2000_2FFF | 12K         | SRAM                   |  |

| 0x5000_0000   | 0x5000_0057 | 88          | SYS_SFR (Include LVDT) |  |

| 0x5000_1000   | 0x5000_1013 | 20          | CRC                    |  |

| 0x5000_2000   | 0x5000_2087 | 136         | GPIOA                  |  |

| 0x5000_2300   | 0x5000_2387 | 136         | GPIOB                  |  |

| 0x5000_2600   | 0x5000_2687 | 136         | GPIOC                  |  |

| 0x5000_2900   | 0x5000_2987 | 136         | GPIOD                  |  |

| 0x5000_3000   | 0x5000_302B | 44          | EXTI                   |  |

| 0x5001_0000   | 0x5001_002F | 48          | FLASH_CTRL             |  |

| 0x5002_0000   | 0x5002_001F | 32          | SPI0                   |  |

| 0x5002_0100   | 0x5002_011F | 32          | SPI1                   |  |

| 0x5003_0000   | 0x5003_001F | 32          | UART0                  |  |

| 0x5003_0100   | 0x5003_011F | 32          | UART1                  |  |

| 0x5003_0200   | 0x5003_021F | 32          | UART2                  |  |

| 0x5003_0300   | 0x5003_031F | 32          | UART3                  |  |

| 0x5003_0400   | 0x5003_041F | 32          | UART4                  |  |

| 0x5004_0000   | 0x5004_0023 | 36          | IIC                    |  |

| 0x5005_0000   | 0x5005_0007 | 8           | WDT                    |  |

| 0x5005_0100   | 0x5005_010B | 12          | PWM0                   |  |

| 0x5005_0200   | 0x5005_020B | 12          | PWM1                   |  |

| 0x5005_0300   | 0x5005_0317 | 24          | DIV                    |  |

| 0x5006_0000   | 0x5006_006F | 112         | TIM0                   |  |

| 0x5006_0100   | 0x5006_016F | 112         | TIM1                   |  |

| 0x5006_0200   | 0x5006_026F | 112         | TIM2                   |  |

| 0x5006_0300   | 0x5006_036F | 112         | TIM3                   |  |

| 0x5006_0400   | 0x5006_046F | 112         | TIM4                   |  |

| 0x5006_0500   | 0x5006_056F | 112         | TIM5                   |  |

| 0x5006_0600   | 0x5006_066F | 112         | TIM6                   |  |

| 0x5006_0700   | 0x5006_076F | 112         | TIM7                   |  |

| 0x5007_0000   | 0x5007_002B | 44          | ADC                    |  |

| 0x5008_0000   | 0x5008_03FF | 1K          | DMA_SRAM               |  |

| 0x5008_0400   | 0x5008_0463 | 100         | DMA_SFR                |  |

| 0x5008_0800   | 0x5008_080B | 12          | DMA_MUX                |  |

Table 1.1 Address division

Note: LVDT address range:  $0x5000\_001C$  to  $0x5000\_0023$

Datasheet Page 5 of449

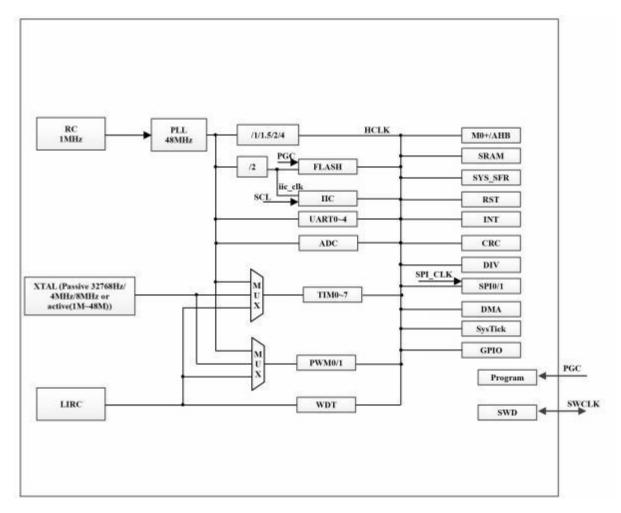

# 1.5. Clock block diagram

Figure 1.3 Clock block diagram

Datasheet Page 6 of449

# 1.6. Selection list

| Model                 |                 | BF7707AM44-<br>LJTX | BF7707AM52_<br>LJTB                | BF7707AM64-<br>LJTA               | BF7707AM64-<br>LJTB                                                                                                                                                 |

|-----------------------|-----------------|---------------------|------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating voltage (V) |                 | 2.6~5.5             | 2.6~5.5                            | 2.6~5.5                           | 2.6~5.5                                                                                                                                                             |

| Operating te          |                 | -40~+105            | -40~+105                           | -40~+105                          | -40~+105                                                                                                                                                            |

| System main           |                 | 48M                 | 48M                                | 48M                               | 48M                                                                                                                                                                 |

| Con                   | re              | ARM<br>Cortex-M0+   | ARM<br>Cortex-M0+                  | ARM<br>Cortex-M0+                 | ARM<br>Cortex-M0+                                                                                                                                                   |

|                       | FLASH           | 128K                | 128K                               | 128K                              | 128K                                                                                                                                                                |

| Memory                | DATA            | 512                 | 512                                | 512                               | 512                                                                                                                                                                 |

| (Bytes)               | SRAM            | 12K                 | 12K                                | 12K                               | 12K                                                                                                                                                                 |

| ** 1                  | GPIO            | 42                  | 50                                 | 60                                | 60                                                                                                                                                                  |

| Universal<br>port     | INT             | 42                  | 50                                 | 60                                | 60                                                                                                                                                                  |

|                       | COM             | 8                   | 8                                  | 8                                 | 8                                                                                                                                                                   |

| T.                    | Advanced timer  | 1                   | 1                                  | 1                                 | 1                                                                                                                                                                   |

| Timer                 | Universal timer | 7                   | 7                                  | 7                                 | 7                                                                                                                                                                   |

|                       | WDT             | 1                   | 1                                  | 1                                 | 1                                                                                                                                                                   |

| PWM                   | PWM0 (16bit)    | 1ch                 | 1ch                                | 1ch                               | 1ch                                                                                                                                                                 |

| module                | PWM1 (16bit)    | 1ch                 | 1ch                                | 1ch                               | 1ch                                                                                                                                                                 |

|                       | IIC             | 1                   | 1                                  | 1                                 | ARM ARM Cortex-M0+  28K 128K 512 512 12K 12K 60 60 60 60 8 8 1 1 7 7 1 1 1ch 1ch 1ch 1ch 1ch 1 1 5 5 2 2 2 18ch 18ch 1 1 1 3ch 3ch 1 1 1 1CFP64 1 10mm, (12mm*12mm, |

| Communica tion module | UART            | 5                   | 5                                  | 5                                 | 5                                                                                                                                                                   |

| tion module           | SPI             | 2                   | 2                                  | 2                                 | 2                                                                                                                                                                   |

| Analog<br>module      | ADC (12bit)     | 11ch                | 15ch                               | 18ch                              | 18ch                                                                                                                                                                |

| System                | DIV<br>(32bit)  | 1                   | 1                                  | 1                                 | 1                                                                                                                                                                   |

| correlation           | DMA             | 3ch                 | 3ch                                | 3ch                               | 3ch                                                                                                                                                                 |

|                       | CRC             | 1                   | 1                                  | 1                                 | 1                                                                                                                                                                   |

| Packa                 | Package         |                     | LQFP52<br>(10mm*10mm,<br>e=0.65mm) | LQFP64<br>(10mm*10mm,<br>e=0.5mm) | (12mm*12mm,                                                                                                                                                         |

Datasheet Page 7 of449

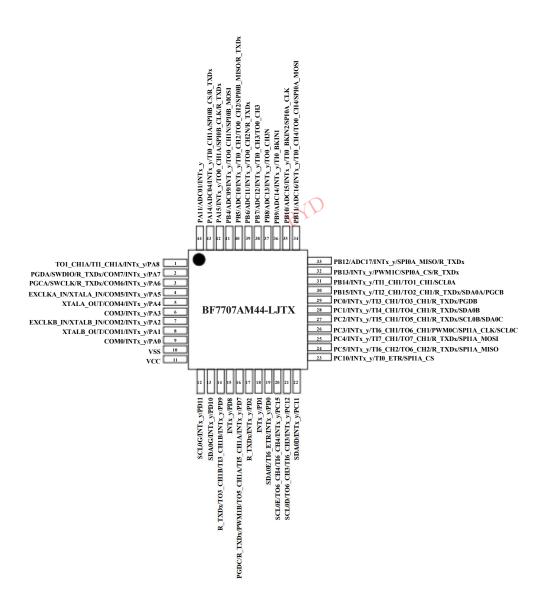

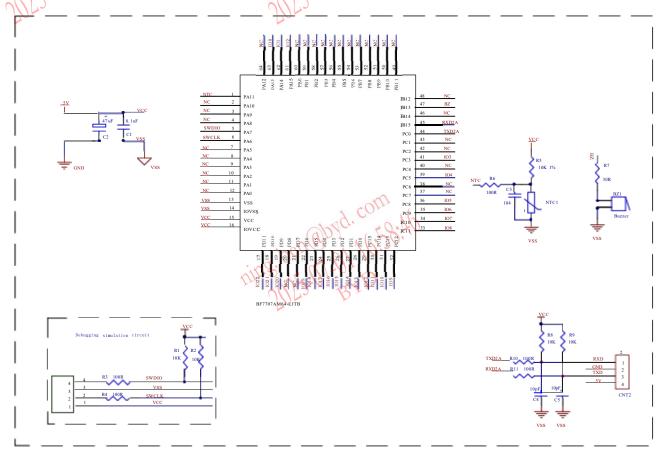

### 1.7. Pin configuration

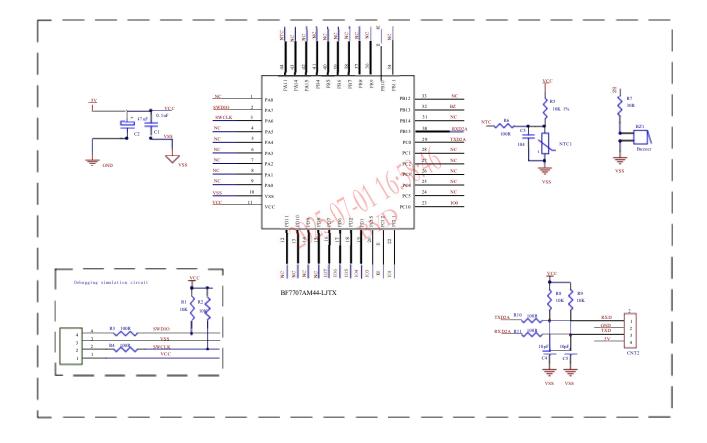

#### 1.7.1. BF7707AM44-LJTX

Figure 1.4 LQFP44 package pin diagram

Datasheet Page 8 of449

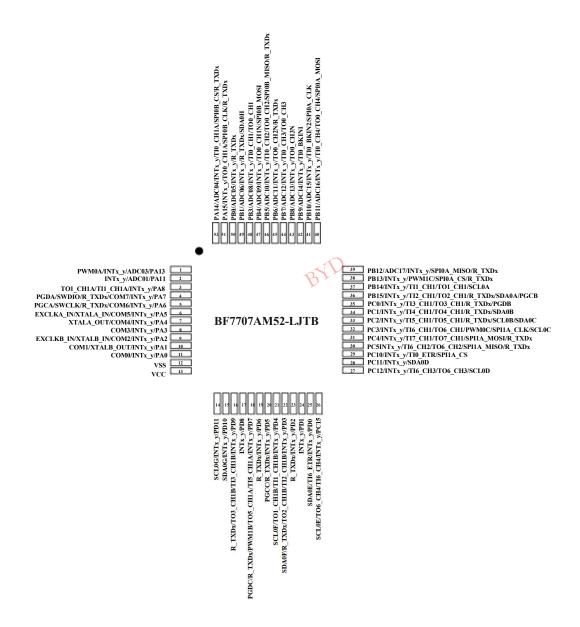

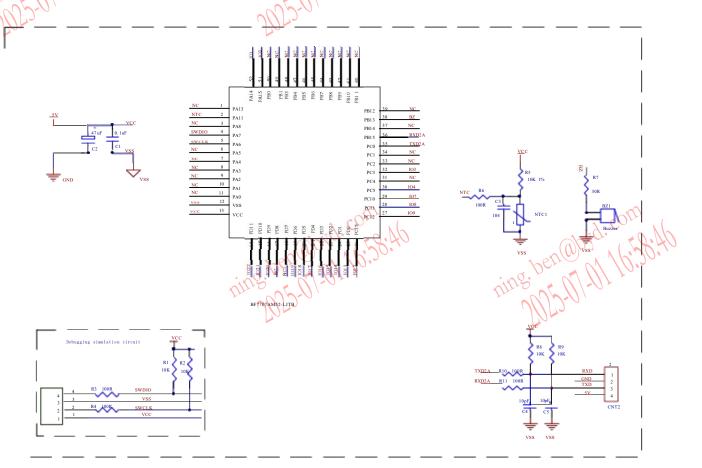

#### 1.7.2. BF7707AM52-LJTB

Figure 1.5 LQFP52 package pin diagram

Note: The INT function can be mapped to INTx\_y (x=0/1/2/3, y=0/1/2/3), and the UART function can be mapped to R\_TXDx (UART  $\mbox{fij}$  RXD/TXD, x=0/1/2/3/4). For more information, refer to "GPIO pin multiplexing configuration Table".

Datasheet Page 9 of449

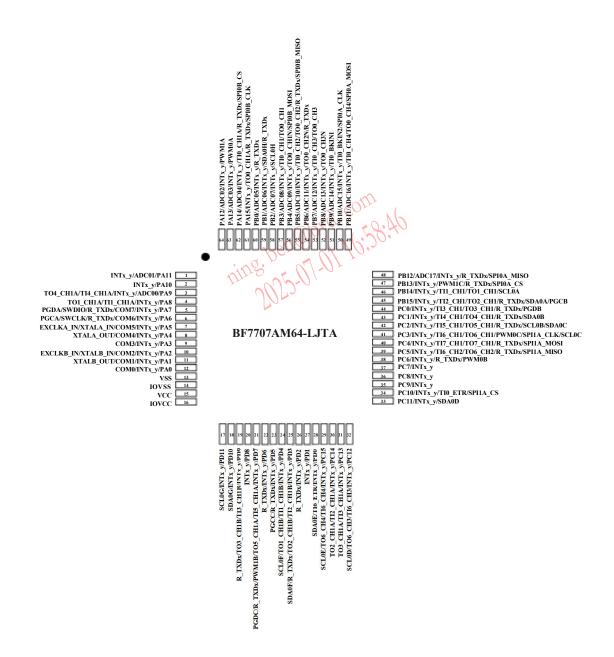

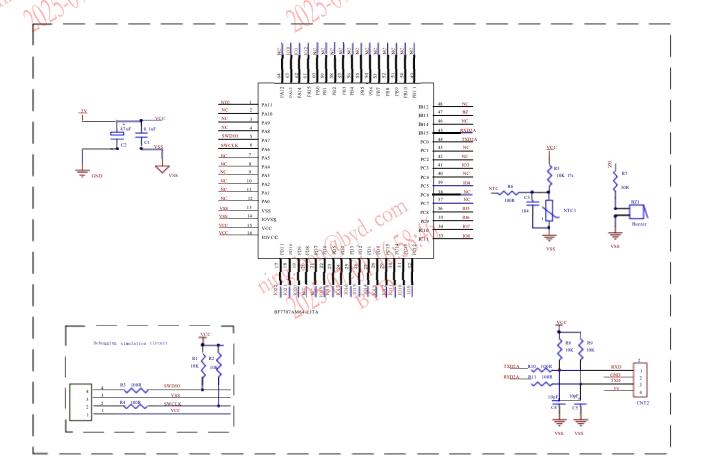

#### 1.7.3. BF7707AM64-LJTA

Figure 1.6 LQFP64 package pin diagram

Datasheet Page 10 of449

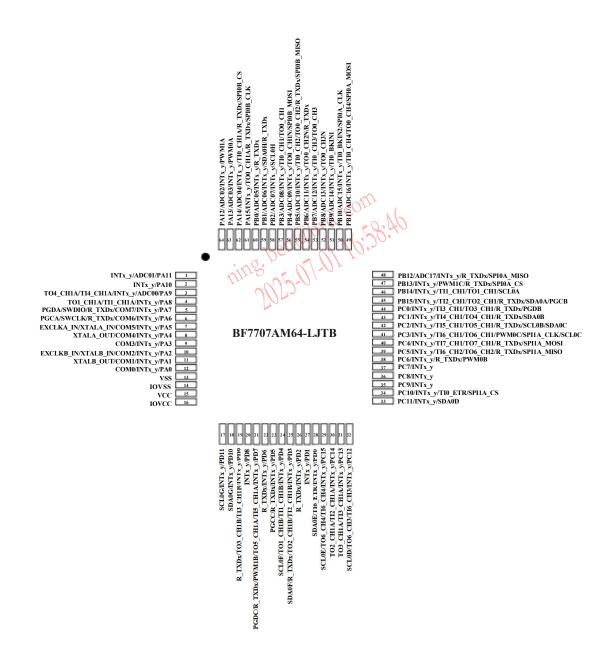

#### 1.7.4. BF7707AM64-LJTB

Figure 1.7 LQFP64 package pin diagram

Datasheet Page 11 of449

# 1.8. Pin description

| BF7707AM64-LJTB | BF7707AM64-LJTA | BF7707AM52-LJTB | BF7707AM44-LJTX | Function description                                                                                                                                                                                          |

|-----------------|-----------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | 1               | 2               | 44              | Default function: GPIO <pa11> Other functions: ADC01: ADC channel 01</pa11>                                                                                                                                   |

| 2               | 2               | -               | _               | INTx_y: External interrupt  Default function: GPIO <pa10> Other functions: INTx_y: External interrupt</pa10>                                                                                                  |

| 3               | 3               | -               | -               | Default function: GPIO <pa9> Other functions: ADC00: ADC channel 00 INTx_y: External interrupt TI4_CH1A: TIM4 input capture channel 1 TO4_CH1A: TIM4 output compare channel 1</pa9>                           |

| 4               | 4               | 3               | 1               | Default function: GPIO <pa8> Other functions: INTx_y: External interrupt</pa8>                                                                                                                                |

| 5               | 5               | 4               | 2               | Default function: GPIO <pa7> Other functions: INTx_y: External interrupt R_TXDx: Serial port transmission/reception SWDIO: Data input/output COM7: Large irrigation current port PGDA: Programming port</pa7> |

| 6               | 6               | 5               | 3               | Default function: GPIO <pa6> Other functions: INTx_y: External interrupt R_TXDx: Serial port transmission/reception SWCLK: Clock signal COM6: Large irrigation current port PGCA: Programming port</pa6>      |

| 7               | 7               | 6               | 4               | Default function: GPIO <pa5> Other functions: INTx_y: External interrupt</pa5>                                                                                                                                |

Datasheet Page 12 of449

|    |    |    |       | COM5: Large irrigation current port         |

|----|----|----|-------|---------------------------------------------|

|    |    |    |       | Default function: GPIO <pa4></pa4>          |

| 0  | 0  | 7  | _     | Other functions: INTx_y: External interrupt |

| 8  | 8  | 7  | 5     | XTALA_OUT: External crystal output          |

|    |    |    |       | COM4: Large irrigation current port         |

|    |    |    |       | Default function: GPIO <pa3></pa3>          |

| 9  | 9  | 8  | 6     | Other functions: INTx_y: External interrupt |

|    |    |    |       | COM3: Large irrigation current port         |

|    |    |    |       | Default function: GPIO <pa2></pa2>          |

|    |    |    |       | Other functions: INTx_y: External interrupt |

| 10 | 10 | 9  | 7     | XTALB_IN: External crystal input            |

|    |    |    |       | EXCLKB_IN: External oscillator input        |

|    |    |    |       | COM2: Large irrigation current port         |

|    |    |    |       | Default function: GPIO <pa1></pa1>          |

| 11 | 11 | 10 | 8     | Other functions: INTx_y: External interrupt |

| 11 | 11 | 10 | ð     | XTALB_OUT: External crystal output          |

|    |    |    |       | COM1: Large irrigation current port         |

|    |    |    |       | Default function: GPIO <pa0></pa0>          |

| 12 | 12 | 11 | 9     | Other functions: INTx_y: External interrupt |

|    |    |    |       | COM0: Large irrigation current port         |

| 13 | 13 | 12 | 10    | Default function: GND <vss></vss>           |

| 14 | 14 | -  | -     | Default function: IOVSS                     |

| 15 | 15 | 13 | 11    | Default function: Power supply <vcc></vcc>  |

| 16 | 16 | -  | -     | Default function: IOVCC                     |

|    |    |    |       | Default function: GPIO <pd11></pd11>        |

| 17 | 17 | 14 | 12    | Other functions: INTx_y: External interrupt |

|    |    |    |       | SCL0G: Serial clock line ofIIC              |

|    |    |    |       | Default function: GPIO <pd10></pd10>        |

| 18 | 18 | 15 | 13    | Other functions: INTx_y: External interrupt |

|    |    |    |       | SDA0G: Serial data line ofIIC               |

|    |    |    |       | Default function: GPIO <pd9></pd9>          |

|    |    |    |       | Other functions: INTx_y: External interrupt |

| 19 | 19 | 16 | 14    | TI3_CH1B: TIM3 input capture channel 1      |

|    |    |    |       | TO3_CH1B: TIM3 output compare channel 1     |

|    |    |    |       | R_TXDx: Serial port transmission/reception  |

| 20 | 20 | 17 | 15    | Default function: GPIO <pd8></pd8>          |

|    |    | 1/ | 13    | Other functions: INTx_y: External interrupt |

|    |    |    |       | Default function: GPIO <pd7></pd7>          |

|    |    |    |       | Other functions: INTx_y: External interrupt |

| 21 | 21 | 18 | 18 16 | TI5_CH1A: TIM5 input capture channel 1      |

|    |    |    |       | TO5_CH1A: TIM5 output compare channel 1     |

|    |    |    |       | R_TXDx: Serial port transmission/reception  |

Datasheet Page 13 of449

|     |      | 160  | 19:40 |                                                                        |       |         |    |                                |    |    |                                     |

|-----|------|------|-------|------------------------------------------------------------------------|-------|---------|----|--------------------------------|----|----|-------------------------------------|

|     | 70   | 100  |       | PWM1B: PWM1 output port                                                |       |         |    |                                |    |    |                                     |

| 205 | 01-0 |      |       | PGDC: Programming port                                                 |       |         |    |                                |    |    |                                     |

| M   |      |      |       | Default function: GPIO <pd6></pd6>                                     |       |         |    |                                |    |    |                                     |

| 22  | 22   | 19   | _     | Other functions: INTx_y: External interrupt                            |       |         |    |                                |    |    |                                     |

|     |      |      |       | R_TXDx: Serial port transmission/reception                             |       |         |    |                                |    |    |                                     |

|     |      |      |       | Default function: GPIO <pd5></pd5>                                     |       |         |    |                                |    |    |                                     |

| 23  | 23   | 20   |       | Other functions: INTx_y: External interrupt                            |       |         |    |                                |    |    |                                     |

| 23  | 23   | 20   | -     | R_TXDx: Serial port transmission/reception                             |       |         |    |                                |    |    |                                     |

|     |      |      |       | PGCC: Programming port                                                 |       |         |    |                                |    |    |                                     |

|     |      |      |       | Default function: GPIO <pd4></pd4>                                     |       |         |    |                                |    |    |                                     |

|     |      |      |       | Other functions: INTx_y: External interrupt                            |       |         |    |                                |    |    |                                     |

| 24  | 24   | 21   | _     | TI1_CH1B: TIM1 input capture channel 1                                 |       |         |    |                                |    |    |                                     |

|     |      |      |       | TO1_CH1B: TIM1 output compare channel 1                                |       |         |    |                                |    |    |                                     |

|     |      |      |       | SCL0F: Serial clock line of IIC                                        |       |         |    |                                |    |    |                                     |

|     |      |      |       | Default function: GPIO <pd3></pd3>                                     |       |         |    |                                |    |    |                                     |

|     |      |      |       | Other functions: INTx y: External interrupt                            |       |         |    |                                |    |    |                                     |

|     |      |      |       | TI2 CH1B: TIM2 input capture channel 1                                 |       |         |    |                                |    |    |                                     |

| 25  | 25   | 22   | -     | TO2_CH1B: TIM2 output compare channel 1                                |       |         |    |                                |    |    |                                     |

|     |      |      |       | R_TXDx: Serial port transmission/reception                             |       |         |    |                                |    |    |                                     |

|     |      |      |       | SDA0F: Serial data line of IIC                                         |       |         |    |                                |    |    |                                     |

|     |      |      |       | Default function: GPIO <pd2></pd2>                                     |       |         |    |                                |    |    |                                     |

| 26  | 26   | 23   | 17    | Other functions: INTx y: External interrupt                            |       |         |    |                                |    |    |                                     |

| -   |      | 25   | 1,    | R TXDx: Serial port transmission/reception                             |       |         |    |                                |    |    |                                     |

|     |      |      |       | Default function: GPIO <pd1></pd1>                                     |       |         |    |                                |    |    |                                     |

| 27  | 27   | 24   | 18    | Other functions: INTx y: External interrupt                            |       |         |    |                                |    |    |                                     |

|     |      |      |       | Default function: GPIO <pd0></pd0>                                     |       |         |    |                                |    |    |                                     |

|     |      |      |       | Other functions: INTx y: External interrupt                            |       |         |    |                                |    |    |                                     |

| 28  | 28   | 8 25 | 25    | 25                                                                     | 28 25 | 28   25 | 25 | 3 25                           | 25 | 19 | TI6_ETRL: TIM6 external trigger pin |

|     |      |      |       |                                                                        |       |         |    | SDA0E: Serial data line of IIC |    |    |                                     |

|     |      |      |       | Default function: GPIO <pc15></pc15>                                   |       |         |    |                                |    |    |                                     |

|     |      |      |       | Other functions: INTx y: External interrupt                            |       |         |    |                                |    |    |                                     |

| 29  | 29   | 26   | 20    | TI6 CH4: TIM6 input capture channel 4                                  |       |         |    |                                |    |    |                                     |

| 29  | 29   | 20   | 20    | _                                                                      |       |         |    |                                |    |    |                                     |

|     |      |      |       | TO6_CH4: TIM6 output compare channel 4 SCL0E: Serial clock line of IIC |       |         |    |                                |    |    |                                     |

|     |      |      |       |                                                                        |       |         |    |                                |    |    |                                     |

|     |      |      |       | Default function: GPIO <pc14></pc14>                                   |       |         |    |                                |    |    |                                     |

| 30  | 30   | _    | _     | Other functions: INTx_y: External interrupt                            |       |         |    |                                |    |    |                                     |

|     |      |      |       | TI2_CH1A: TIM2 input capture channel 1                                 |       |         |    |                                |    |    |                                     |

|     |      |      |       | TO2_CH1A: TIM2 output compare channel 1                                |       |         |    |                                |    |    |                                     |

|     |      |      |       | Default function: GPIO <pc13></pc13>                                   |       |         |    |                                |    |    |                                     |

| 31  | 31   | _    | _     | Other functions: INTx_y: External interrupt                            |       |         |    |                                |    |    |                                     |

|     |      |      |       | TI3_CH1A: TIM3 input capture channel 1                                 |       |         |    |                                |    |    |                                     |

|     |      |      |       | TO3_CH1A: TIM3 output compare channel 1                                |       |         |    |                                |    |    |                                     |

Datasheet Page 14 of449

|     |            | ( ) | 19:10 |                                             |  |  |  |  |  |

|-----|------------|-----|-------|---------------------------------------------|--|--|--|--|--|

|     | 70         | 10. |       | Default function: GPIO <pc12></pc12>        |  |  |  |  |  |

| 205 | 01-0       |     |       | Other functions: INTx_y: External interrupt |  |  |  |  |  |

| 32  | 32         | 27  | 21    | TI6_CH3: TIM6 input capture channel 3       |  |  |  |  |  |

|     |            |     |       | TO6_CH3: TIM6 output compare channel 3      |  |  |  |  |  |

|     |            |     |       | SCL0D: Serial clock line of IIC             |  |  |  |  |  |

|     |            |     |       | Default function: GPIO <pc11></pc11>        |  |  |  |  |  |

| 33  | 33         | 28  | 22    | Other functions: INTx_y: External interrupt |  |  |  |  |  |

|     |            |     |       | SDA0D: Serial data line ofIIC               |  |  |  |  |  |

|     |            |     |       | Default function: GPIO <pc10></pc10>        |  |  |  |  |  |

| 2.4 | 2.4        | 20  | 22    | Other functions: INTx_y: External interrupt |  |  |  |  |  |

| 34  | 34         | 29  | 23    | TI0_ETR: TIM0 external trigger pin          |  |  |  |  |  |

|     |            |     |       | SPI1A_CS: SPI chip selection signal         |  |  |  |  |  |

| 2.5 | 2.5        |     |       | Default function: GPIO <pc9></pc9>          |  |  |  |  |  |

| 35  | 35         | -   | -     | Other functions: INTx_y: External interrupt |  |  |  |  |  |

| 2.6 | 2.6        |     |       | Default function: GPIO <pc8></pc8>          |  |  |  |  |  |

| 36  | 36         | -   | -     | Other functions: INTx y: External interrupt |  |  |  |  |  |

|     |            |     |       | Default function: GPIO <pc7></pc7>          |  |  |  |  |  |

| 37  | 37         | -   | -     | Other functions: INTx_y: External interrupt |  |  |  |  |  |

|     |            |     |       | Default function: GPIO <pc6></pc6>          |  |  |  |  |  |

|     |            |     |       | Other functions: INTx y: External interrupt |  |  |  |  |  |

| 38  | 38         | -   | -     | R_TXDx: Serial port transmission/reception  |  |  |  |  |  |

|     |            |     |       | PWM0B: PWM0 output port                     |  |  |  |  |  |

|     |            |     |       | Default function: GPIO <pc5></pc5>          |  |  |  |  |  |

|     |            |     |       | Other functions: INTx y: External interrupt |  |  |  |  |  |

|     |            |     |       | TI6_CH2: TIM6 input capture channel 2       |  |  |  |  |  |

| 39  | 39         | 30  | 24    | TO6_CH2: TIM6 output compare channel 2      |  |  |  |  |  |

|     |            |     |       | R TXDx: Serial port transmission/reception  |  |  |  |  |  |

|     |            |     |       | SPI1A MISO: SPI master data input           |  |  |  |  |  |

|     |            |     |       | Default function: GPIO <pc4></pc4>          |  |  |  |  |  |

|     |            |     |       | Other functions: INTx y: External interrupt |  |  |  |  |  |

|     |            |     |       | TI7 CH1: TIM7 input capture channel 1       |  |  |  |  |  |

| 40  | 40         | 31  | 25    | TO7_CH1: TIM7 output compare channel 1      |  |  |  |  |  |

|     |            |     |       | R_TXDx: Serial port transmission/reception  |  |  |  |  |  |

|     |            |     |       | SPI1A MOSI: SPI master data output          |  |  |  |  |  |

|     |            |     |       | Default function: GPIO <pc3></pc3>          |  |  |  |  |  |

|     |            |     |       | Other functions: INTx y: External interrupt |  |  |  |  |  |

|     |            |     |       | TI6_CH1: TIM6 input capture channel 1       |  |  |  |  |  |

| 41  | 41         | 32  | 26    | TO6_CH1: TIM6 output compare channel 1      |  |  |  |  |  |

| 71  | 11         | 52  | 20    | SCL0C: Serial clock line of IIC             |  |  |  |  |  |

|     |            |     |       | SPI1A CLK: SPI clock line                   |  |  |  |  |  |

|     |            |     |       | PWM0C: PWM0 output port                     |  |  |  |  |  |

| 42  | 42         | 33  | 27    | Default function: GPIO <pc2></pc2>          |  |  |  |  |  |

| 42  | <b>+</b> 4 | 33  | 41    | Default fulletion. Of 10 \rection 102/      |  |  |  |  |  |

Datasheet Page 15 of449

|       | 10.40 |       |    |                                             |  |  |  |

|-------|-------|-------|----|---------------------------------------------|--|--|--|

|       | 10    | 1,70. |    | Other functions: INTx_y: External interrupt |  |  |  |

| 200   | 0.1-0 | >     |    | TI5_CH1: TIM5 input capture channel 1       |  |  |  |

| UNITY |       |       |    | TO5_CH1: TIM5 output compare channel 1      |  |  |  |

|       |       |       |    | R_TXDx: Serial port transmission/reception  |  |  |  |

|       |       |       |    | SDA0C: Serial data line ofIIC               |  |  |  |

|       |       |       |    | SCL0B: Serial clock line of IIC             |  |  |  |

|       |       |       |    | Default function: GPIO <pc1></pc1>          |  |  |  |

|       |       |       |    | Other functions: INTx_y: External interrupt |  |  |  |

| 43    | 43    | 34    | 28 | TI4_CH1: TIM4 input capture channel 1       |  |  |  |

| 43    | 43    | 34    | 20 | TO4_CH1: TIM4 output compare channel 1      |  |  |  |

|       |       |       |    | R_TXDx: Serial port transmission/reception  |  |  |  |

|       |       |       |    | SDA0B: Serial data line ofIIC               |  |  |  |

|       |       |       |    | Default function: GPIO <pc0></pc0>          |  |  |  |

|       |       |       |    | Other functions: INTx_y: External interrupt |  |  |  |

| 44    | 44    | 35    | 29 | TI3_CH1: TIM3 input capture channel 1       |  |  |  |

| 77    | 44    | 33    | 29 | TO3_CH1: TIM3 output compare channel 1      |  |  |  |

|       |       |       |    | R_TXDx: Serial port transmission/reception  |  |  |  |

|       |       |       |    | PGDB: Programming port                      |  |  |  |

|       |       |       |    | Default function: GPIO <pb15></pb15>        |  |  |  |

|       |       |       |    | Other functions: INTx_y: External interrupt |  |  |  |

|       |       |       |    | TI2_CH1: TIM2 input capture channel 1       |  |  |  |

| 45    | 45    | 36    | 30 | TO2_CH1: TIM2 output compare channel 1      |  |  |  |

|       |       |       |    | R_TXDx: Serial port transmission/reception  |  |  |  |

|       |       |       |    | SDA0A: Serial data line ofIIC               |  |  |  |

|       |       |       |    | PGCB: Programming port                      |  |  |  |

|       |       |       |    | Default function: GPIO <pb14></pb14>        |  |  |  |

|       |       |       |    | Other functions: INTx_y: External interrupt |  |  |  |

| 46    | 46    | 37    | 31 | TI1_CH1: TIM1 input capture channel 1       |  |  |  |

|       |       |       |    | TO1_CH1: TIM1 output compare channel 1      |  |  |  |

|       |       |       |    | SCL0A: Serial clock line ofIIC              |  |  |  |

|       |       |       |    | Default function: GPIO <pb13></pb13>        |  |  |  |

|       |       |       |    | Other functions: INTx_y: External interrupt |  |  |  |

| 47    | 47    | 38    | 32 | R_TXDx: Serial port transmission/reception  |  |  |  |

|       |       |       |    | SPI0A_CS: SPI chip selection signal         |  |  |  |

|       |       |       |    | PWM1C: PWM1 output port                     |  |  |  |

|       |       |       |    | Default function: GPIO <pb12></pb12>        |  |  |  |

|       |       |       |    | Other functions: ADC17: ADC channel 17      |  |  |  |

| 48    | 48    | 39    | 33 | INTx_y: External interrupt                  |  |  |  |

|       |       |       |    | R_TXDx: Serial port transmission/reception  |  |  |  |

|       |       |       |    | SPI0A_MISO: SPI master data input           |  |  |  |

| 49    | 49    | 40    | 34 | Default function: GPIO <pb11></pb11>        |  |  |  |

|       |       |       | .  | Other functions: ADC16: ADC channel 16      |  |  |  |

Datasheet Page 16 of449

|       | abye                         |             | 8.70    |                                             |

|-------|------------------------------|-------------|---------|---------------------------------------------|

| pen   | 2 1/                         | ' <i>Jo</i> | ) -     | INTx_y: External interrupt                  |

| 14:05 | $\mathcal{U}_{i}/\gamma_{i}$ | >           |         | TI0_CH4: TIM0 input capture channel 4       |

| 100   |                              |             |         | TO0_CH4: TIM0 output compare channel 4      |

|       |                              |             |         | SPI0A_MOSI: SPI master data output          |

|       |                              |             |         | Default function: GPIO <pb10></pb10>        |

|       |                              |             |         | Other functions: ADC15: ADC channel 15      |

| 50    | 50                           | 41          | 35      | INTx_y: External interrupt                  |

|       |                              |             |         | TI0_BKIN2: TIM0 brake input pin             |

|       |                              |             |         | SPI0A_CLK: SPI clock line                   |

|       |                              |             |         | Default function: GPIO <pb9></pb9>          |

| 51    | 51                           | 42          | 36      | Other functions: ADC14: ADC channel 14      |

| 31    | 31                           | 42          | 30      | INTx_y: External interrupt                  |

|       |                              |             |         | TI0_BKIN1: TIM0 brake input pin             |

|       |                              |             |         | Default function: GPIO <pb8></pb8>          |

|       |                              |             |         | Other functions: ADC13: ADC channel 13      |

| 52    | 52                           | 43          | 37      | INTx_y: External interrupt                  |

|       |                              |             |         | TO0_CH3N: TIM0 complementary output compare |

|       |                              |             |         | channel 3                                   |

|       |                              |             |         | Default function: GPIO <pb7></pb7>          |

|       |                              |             |         | Other functions: ADC12: ADC channel 12      |

| 53    | 53                           | 44          | 38      | INTx_y: External interrupt                  |

|       |                              |             |         | TI0_CH3: TIM0 input capture channel 3       |

|       |                              |             |         | TO0_CH3: TIM0 output compare channel 3      |

|       |                              |             |         | Default function: GPIO <pb6></pb6>          |

|       |                              |             |         | Other functions: ADC11: ADC channel 11      |

| 54    | 54                           | 45          | 39      | INTx_y: External interrupt                  |

|       |                              | 1.5         | 37      | TO0_CH2N: TIM0 complementary output compare |

|       |                              |             |         | channel 2                                   |

|       |                              |             |         | R_TXDx: Serial port transmission/reception  |

|       |                              |             |         | Default function: GPIO <pb5></pb5>          |

|       |                              |             |         | Other functions: ADC10: ADC channel 10      |

|       |                              |             |         | INTx_y: External interrupt                  |

| 55    | 55                           | 46          | 40      | TI0_CH2: TIM0 input capture channel 2       |

|       |                              |             |         | TO0_CH2: TIM0 output compare channel 2      |

|       |                              |             |         | R_TXDx: Serial port transmission/reception  |

|       |                              |             |         | SPI0B_MISO: SPI master data input           |

|       |                              |             |         | Default function: GPIO <pb4></pb4>          |

|       |                              |             |         | Other functions: ADC09: ADC channel 09      |

| 56    | 56                           | 47          | 47   41 | INTx_y: External interrupt                  |

|       |                              | • •         |         | TO0_CH1N: TIM0 complementary output compare |

|       |                              |             |         | channel 1                                   |

|       |                              |             |         | SPI0B_MOSI: SPI master data output          |

Datasheet Page 17 of449

| (    | Mole                         | 15  | 3.40     |                                             |

|------|------------------------------|-----|----------|---------------------------------------------|

| pen  | ()<br>()                     | 10. | <b>)</b> | Default function: GPIO <pb3></pb3>          |

| 3.05 | $\mathcal{U}_{L}/\sigma_{D}$ | >   |          | Other functions: ADC08: ADC channel 08      |

| 57   | 7 57 48 -                    |     |          | INTx_y: External interrupt                  |

|      |                              |     |          | TI0_CH1: TIM0 input capture channel 1       |

|      |                              |     |          | TO0_CH1: TIM0 output compare channel 1      |

|      |                              |     |          | Default function: GPIO <pb2></pb2>          |

| 58   | 58                           |     |          | Other functions: ADC07: ADC channel 07      |

| 38   | 38                           | -   | -        | INTx_y: External interrupt                  |

|      |                              |     |          | SCL0H: Serial clock line ofIIC              |

|      |                              |     |          | Default function: GPIO <pb1></pb1>          |

|      |                              |     |          | Other functions: ADC06: ADC channel 06      |

| 59   | 59                           | 49  | -        | INTx_y: External interrupt                  |

|      |                              |     |          | R_TXDx: Serial port transmission/reception  |

|      |                              |     |          | SDA0H: Serial data line ofIIC               |

|      |                              |     |          | Default function: GPIO <pb0></pb0>          |

| 60   | 60                           | 50  |          | Other functions: ADC05: ADC channel 05      |

| 60   | 00                           | 50  | -        | INTx_y: External interrupt                  |

|      |                              |     |          | R_TXDx: Serial port transmission/reception  |

|      |                              |     |          | Default function: GPIO <pa15></pa15>        |

|      |                              |     |          | Other functions: INTx_y: External interrupt |

| 61   | 61                           | 51  | 42       | TO0_CH1A: TIM0 output compare channel 1     |

|      |                              |     |          | R_TXDx: Serial port transmission/reception  |

|      |                              |     |          | SPI0B_CLK: SPI clock line                   |

|      |                              |     |          | Default function: GPIO <pa14></pa14>        |

|      |                              |     |          | Other functions: ADC04: ADC channel 04      |

| 62   | 62                           | 52  | 43       | INTx_y: External interrupt                  |

| 02   | 02                           | 34  | 43       | TI0_CH1A: TIM0 input capture channel 1      |

|      |                              |     |          | R_TXDx: Serial port transmission/reception  |

|      |                              |     |          | SPI0B_CS: SPI chip selection signal         |

|      |                              |     |          | Default function: GPIO <pa13></pa13>        |

| 63   | 63                           | 1   |          | Other functions: ADC03: ADC channel 03      |

| 03   | 03                           | 1   | -        | INTx_y: External interrupt                  |

|      |                              |     |          | PWM0A: PWM0 output port                     |

|      |                              |     |          | Default function: GPIO <pa12></pa12>        |

| 64   | 64                           |     |          | Other functions: ADC02: ADC channel 02      |

| 04   | 04                           | -   | -        | INTx_y: External interrupt                  |

|      |                              |     |          | PWM1A: PWM1 output port                     |

Datasheet Page 18 of449

# Chapter 2 Electrical characteristics

### 2.1. Limit parameters

| Cross had | D                                    | Test ( | Condition | Min     | Tymiaal | M       | T134                 |

|-----------|--------------------------------------|--------|-----------|---------|---------|---------|----------------------|

| Symbol    | Parameter                            | VCC    | Condition | Min     | Typical | Max     | Unit                 |

| VCC       | Supply voltage when operating        | ı      | -         | VSS+2.6 | -       | VSS+5.5 | V                    |

| Tstg      | Storage temperature                  | ı      | -         | -40     | -       | 125     | °C                   |

| Та        | Operating temperature                | -      | -         | -40     | -       | 105     | $^{\circ}\mathrm{C}$ |

| Vin       | I/O input voltage                    | -      | -         | VSS-0.5 | -       | VCC+0.5 | V                    |

| Iola      | IoL total current                    | -      | -         |         | 130     |         | mA                   |

| Іона      | Ioh total current                    | -      | -         |         | -130    |         | mA                   |

| ESD(HBM)  | Port electrostatic discharge voltage | -      | -         | -6      | -       | 6       | kV                   |

Note: Exceeding the range specified by the limit parameters will cause damage to the chip. It is impossible to predict the working state of the chip outside the above marked range, and if it works under the conditions outside the marked range for a long time, it may affect the reliability of the chip.

Datasheet Page 19 of449

### 2.2. AC characteristics

|                   | 1 CON                    |             |              | 16   | Di          | 77077    |         | 1/2  |

|-------------------|--------------------------|-------------|--------------|------|-------------|----------|---------|------|

| 1-60(0)           | 16:28:40                 |             | 16:58        | 9.40 |             |          | 16:58   | 140  |

| 2.2. AC           | characteristi            | cs          | 25-07-07 10  |      | 7           | 125-07-9 | BAD     |      |

| Cyrrah al         | Danamatan                | Test C      | onditions    | M:   | Tymical     | Max      | T T 34  |      |

| Symbol            | Parameter                | VCC         | Temperature  | Min  | Typical     | Max      | Unit    |      |

|                   | Lutama1                  | <b>53</b> 7 | -20°C~65°C   | -1%  | 1           | +1%      |         |      |

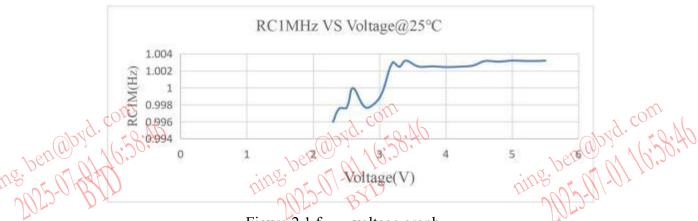

| L C               | Internal                 | 5V          | -40°C ~105°C | -3%  | 1           | +3%      | MII-    |      |

| $f_{RC1M}$        | high-speed RC oscillator | 2.6V~5.5V   | 25°C         | -1%  | 1           | +1%      | MHz     |      |

|                   |                          |             | -40°C ~105°C | -3%  | 1           | +3%      |         |      |

|                   |                          | <b>53</b> 7 | -20°C~65°C   | -1%  | 48/32/24/12 | +1%      |         |      |

| C                 | C411-                    | 5V          | -40°C ~105°C | -3%  | 48/32/24/12 | +3%      |         |      |

| f <sub>HCLK</sub> | System clock             | 2 () 5 5 1  | 25°C         | -1%  | 48/32/24/12 | +1%      | MHz     | . (  |

|                   |                          | 2.6V~5.5V   | -40°C ~105°C | -3%  | 48/32/24/12 | +3%      | 120     | OH.  |

|                   | _                        | <b>53</b> 7 | 25°C         | -10% | 32          | +10%     | 1 10:30 | )• . |

| C                 | Internal low             | 5V          | -40°C ~105°C | -25% | 32          | +25%     | 1-11-   |      |

| flirc             | speed RC                 | 2 (XI 5 5XI | 25°C         | -20% | 32          | +20%     | kHz     |      |

|                   | oscillator               | 2.6V~5.5V   | -40°C ~105°C | -30% | 32          | +30%     |         |      |

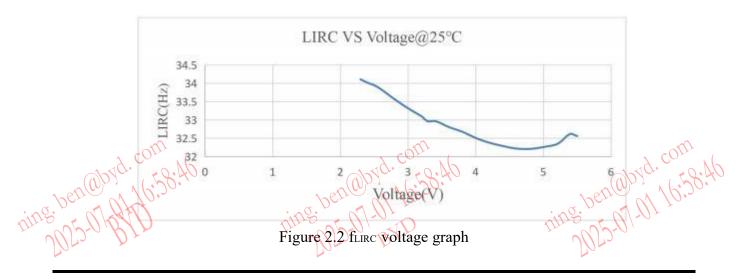

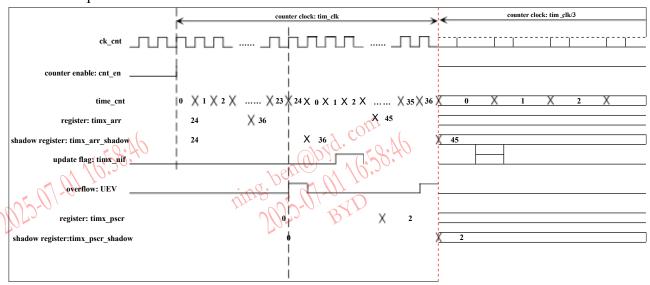

Figure 2.1 frcim voltage graph

Datasheet Page 20 of449

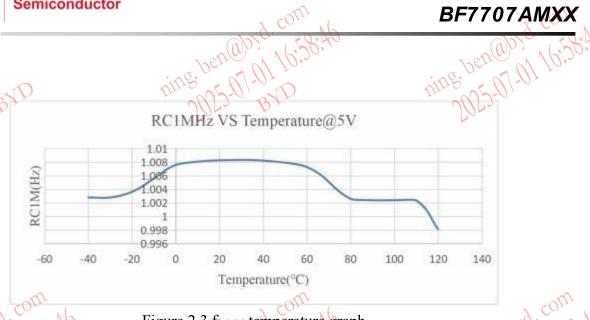

Figure 2.3 frcim temperature graph

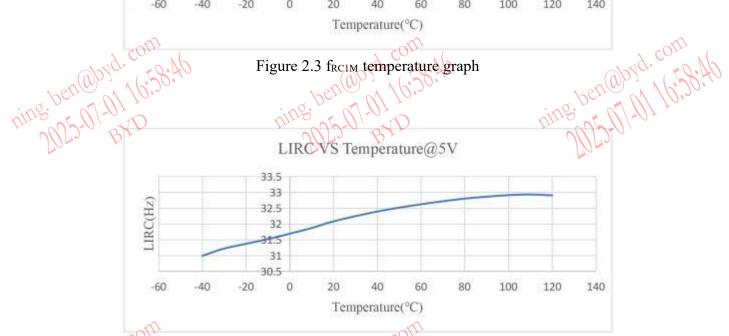

Figure 2.4 f<sub>LIRC</sub> temperature graph

ning, ben abyd, com

Page 21 of449 Datasheet

# 2.3. DC characteristics

Ta=25°C

|                    |                        | Те       | st Condition                                            |         |         |         | 1=25°C |

|--------------------|------------------------|----------|---------------------------------------------------------|---------|---------|---------|--------|

| Symbol             | Parameter              | VCC      | Condition                                               | Min     | Typical | Max     | Unit   |

| VCC                | Operating voltage      | _        | - Condition                                             | 2.6     | _       | 5.5     | V      |

| YCC                |                        | 3.3V     | f <sub>RC1M</sub> /PLL on,<br>f <sub>HCLK</sub> =48MHz, | -       | 5.4     | 7       |        |

|                    |                        | 5V       | flire on, all peripherals off                           | -       | 5.5     | 7.2     |        |

|                    |                        | 3.3V     | f <sub>RC1M</sub> /PLL on,<br>f <sub>HCLK</sub> =32MHz, | -       | 4.3     | 5.6     |        |

| Гор                | Active mode            | 5V       | func on, all peripherals off                            | -       | 4.4     | 5.7     | mA     |

|                    | current                | 3.3V     | f <sub>RC1M</sub> /PLL on,<br>f <sub>HCLK</sub> =24MHz, | -       | 3.9     | 5.1     | IIIA   |

|                    |                        | 5V       | flire on, all peripherals off                           | -       | 4.0     | 5.2     |        |

|                    |                        | 3.3V     | f <sub>RC1M</sub> /PLL on,<br>f <sub>HCLK</sub> =12MHz, | -       | 3.0     | 3.9     |        |

|                    |                        | 5V       | flire on, all peripherals off                           | -       | 3.1     | 4.0     |        |

| ${ m I}_{ m STB0}$ | Idle mode 0            | 3.3V     | f <sub>RC1M</sub> /PLL on,<br>f <sub>HCLK</sub> off,    | -       | 1.8     | 2.3     | mA     |

| 1STB0              | current                | 5V       | flire on, all peripherals off                           | -       | 1.9     | 2.5     | ША     |

| I.m.               | Idle mode 1            | 3.3V     | frcim/PLL/fhclk                                         | -       | 6.6     | -       |        |

| I <sub>STB1</sub>  | current                | 5V       | on, f <sub>LIRC</sub> on, all peripherals off           | -       | 5.6     | -       | μA     |

| $V_{\text{IL}}$    | Input low voltage      | 2.6~5.5V | -                                                       | -       | -       | 0.3*VCC | V      |

| $V_{\text{IH}}$    | Input high voltage     | 2.6~5.5V | -                                                       | 0.7*VCC | -       | -       | V      |

| $V_{\text{INTL}}$  | INT input low voltage  | 2.6~5.5V | -                                                       | -       | -       | 0.3*VCC | V      |

| $V_{\text{INTH}}$  | INT input high voltage | 2.6~5.5V | -                                                       | 0.7*VCC | -       | -       | V      |

| Vol                | Output low voltage     | 5V       | I <sub>OL</sub> =66mA                                   | -       | -       | 0.1*VCC | V      |

| Vон                | Output high voltage    | 5V       | I <sub>OH</sub> =16mA                                   | 0.9*VCC | -       | -       | V      |

| Iol                | IO sink current        | 5V       | V <sub>OL</sub> =0.1VCC                                 | 49      | 66      | 91      | mA     |

Datasheet Page 22 of449

| Тон               | IO source current                        | 5V | V <sub>OH</sub> =0.9VCC | 12 | 16  | 22 | mA |

|-------------------|------------------------------------------|----|-------------------------|----|-----|----|----|

| Ісом              | PA0-PA7 high current                     | 5V | V <sub>OL</sub> =0.1VCC | -  | 130 | -  | mA |

| I <sub>Leak</sub> | Input leakage current                    | 5V | -                       | -  | 1   | 5  | μΑ |

| R <sub>PH</sub>   | IO/RST_N<br>internal pull-up<br>resistor | 5V | -                       | 8  | 12  | 16 | kΩ |

|             | Cymhol                    | Parameter     |     | <b>Test Condition</b>               | Min    | Tymical | Max   | Unit                |  |

|-------------|---------------------------|---------------|-----|-------------------------------------|--------|---------|-------|---------------------|--|

|             | Symbol                    | rarameter     | VCC | Condition                           | IVIIII | Typical | Max   | Omt                 |  |

|             | 1                         | COLLI         |     | f <sub>HCLK</sub> =48MHz, ADC clock |        |         | 1     | $CO_{\overline{M}}$ |  |

|             | IADC                      | ADC operating | 5V  | select 12MHz, enable                | _      | 4.4     | 100 V | mΑ                  |  |

|             | pen (m)                   | current       |     | ADC, open one channel               |        | - be    | 200   | //0:3               |  |

| MINE        |                           |               | rin | f <sub>HCLK</sub> =48MHz, enable    |        | ning.   | 1/7   | 77                  |  |

| <b>&gt;</b> | $I_{PWM}$                 | PWM operating | 5V  | PWM0, output 4kHz                   | _      | 0.35    | 3-0,  | mA                  |  |

|             |                           | current       |     | waveform                            |        |         |       |                     |  |

|             |                           |               |     | f <sub>HCLK</sub> =48MHz, enable    |        |         |       |                     |  |

|             | $I_{LVDT}$ LVDT operating |               | 5V  | LVDT, configure                     | _      | 5.0     | -     | mA                  |  |

|             |                           | current       |     | detection parameter 2.7V            |        |         |       |                     |  |

### 2.4. ADC characteristics

|    |                   | com                             |       | com                                                                                        |     | Ta=25°C |      |      |

|----|-------------------|---------------------------------|-------|--------------------------------------------------------------------------------------------|-----|---------|------|------|

| 4  | Symbol            | Parameter                       | VCC \ | est Condition  Condition                                                                   | Min | Typical | Max  | Unit |

| 5. | VADC              | Supply voltage                  | 240g. | 1 W 1 1 1                                                                                  | 2.6 | -7178   | 5.5  | V    |

|    | NR                | Precision                       | - 0   | 152-0, -                                                                                   | -   | 9       | 10   | Bit  |

|    | V <sub>ADCI</sub> | ADC input voltage               | _     | <del>-</del>                                                                               | VSS |         | VREF | V    |

|    | R <sub>ADCI</sub> | ADC input resistance            | 5V    | -                                                                                          | 0.7 | 0.8     | 3.7  | kΩ   |

|    | Iadc              | ADC operating current           | 5V    | f <sub>HCLK</sub> =48MHz,<br>ADC clock select<br>12MHz, enable<br>ADC, open one<br>channel | -   | 4.4     |      | mA   |

|    | I <sub>ADCI</sub> | A/D input current               | _     | -                                                                                          | _   | -       | 1    | μΑ   |

|    | DNL               | Differential nonlinearity error | 5V    | -                                                                                          | -   | ±4      | ±6   | LSB  |

|    | INL Y             | Integral nonlinearity error     | 5V    | -                                                                                          | _   | ±4      | ±6   | LSB  |

Page 23 of449 Datasheet

|                  | ( , 17) [ ]         |   |   |       |      |    |         |

|------------------|---------------------|---|---|-------|------|----|---------|

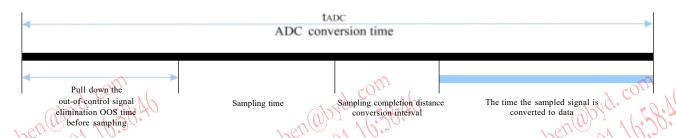

| t2               | ADC sampling time   | - | - | 0.212 | -    | -  | μs      |

| t <sub>ADC</sub> | ADC conversion time | ı | - | 0.583 | -    | -  | μs      |

| RESO             | Resolution          | _ | _ |       | 8/12 |    | Bit     |

| Nadc             | Input channel       | - | - | 1     | -    | 18 | Channel |

# 2.5. Temperature sensor characteristics

| Cross b al | Danamatan              | Test  | Condition | Min | Teminal | Max   | TT34  |

|------------|------------------------|-------|-----------|-----|---------|-------|-------|

| Symbol     | Parameter              | VCC   | Condition | Min | Typical | Max   | Unit  |

| Avg_slope  | Temperature mean slope |       | 19 0.V    | 0 - | 3.227   | - 🕥   | mV/°C |

| 1250 (O) 1 | Linearity of the       | Devio | 10:20.    |     |         | ±10°C |       |

| Tr (       | temperature sensor     | 5 - 1 |           | -   | - 010   | ±10-C |       |

# 2.6. Memory characteristics

Ta=25°C

| Cymhal              | Parameter             |     | <b>Test Condition</b>                                                                                                                                       | Min  | Tymical | Mov | Unit  |

|---------------------|-----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-----|-------|

| Symbol              | Parameter             | VCC | Condition                                                                                                                                                   | Min  | Typical | Max | Unit  |

| EC                  | Erase and write times | 5V  | -                                                                                                                                                           | 100k | -       | -   | Cycle |

| t <sub>RET</sub>    | Data retention period | -   | -                                                                                                                                                           | 100  | -       | -   | Year  |

| t <sub>PROG</sub>   | Word programming time | 5V  | -                                                                                                                                                           | ı    | 46      | -   | μs    |

| terase              | Page erase time       | 5V  | -                                                                                                                                                           | -    | 4.5     | -   | ms    |

| t <sub>MERASE</sub> | Whole chip erase time | 5V  | -                                                                                                                                                           | ı    | 30      | -   | ms    |

| I <sub>ERASE</sub>  | Page erase current    | 5V  | f <sub>HCLK</sub> =48MHz, in the while,<br>the main memory block is<br>page erased, turn offall<br>other functions. Total chip<br>power consumption.        | -    | 6.3     | -   | mA    |

| Iprog               | Programming current   | 5V  | f <sub>HCLK</sub> =48MHz, in the while,<br>a word is written to the main<br>memory block, turn off all<br>other functions. Total chip<br>power consumption. | -    | 6.3     | -   | mA    |

Datasheet Page 24 of449

## Chapter 3 System control (SYS\_CTRL)

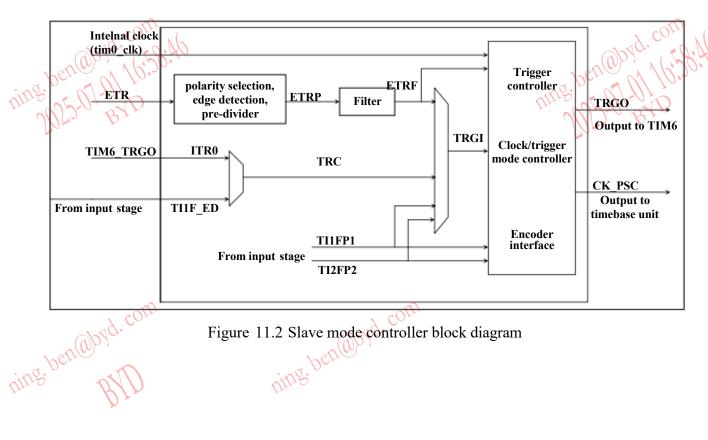

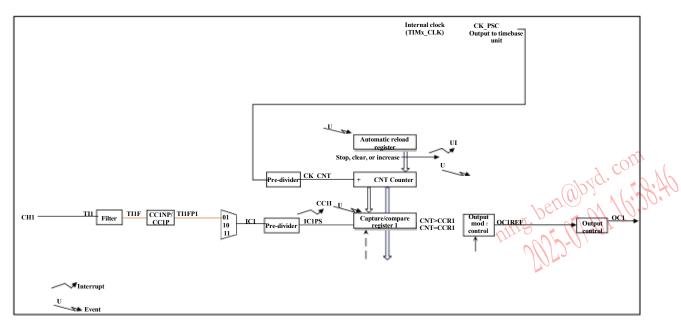

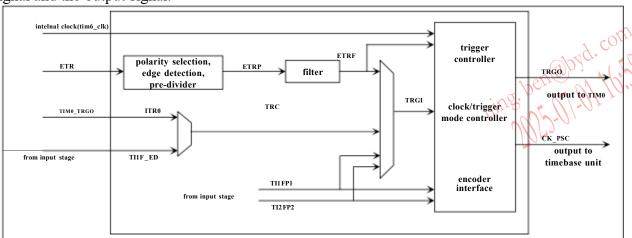

#### 3.1. Clock description

The clock control module mainly controls the system clock and peripheral clock. It can configure different system clock frequency divisions, and can enable or disable peripheral clocks.

#### **Clock source:**

- Internal high-speed RC oscillator: RC 1MHz

- Internal low-speed RC oscillator: LIRC 32kHz

- External crystal oscillator XTAL: Passive crystal oscillator (32768Hz/4MHz/8MHz) and active crystal oscillator (1MHz~48MHz)

- RC1M frequency multiplication to get PLL clock: PLL frequency multiplied clock

#### The BF7707AMXX series clocks are defined as follows:

- RC1M: Internal high-speed RC oscillator, frequency multiplication to get PLL48M clock, it provides the clock for the core and its peripheral equipment, and manages the low-power mode by clock gating and multistage prescaler.

- PLL48M: System clock source, TIM/ADC/PWM/UART module working clock, and external interrupt filtering clock source.

- **HCLK:** System clock, AHB bus peripheral clock, 48MHz/32MHz/24MHz/12MHz frequency optional.

- PLL48M divide by 2: FLASH programming clock, IIC digital filter clock and IIC master working clock(iic\_clk).

- LIRC 32kHz: Internal low-speed RC oscillator, WDT/TIM/PWM module clock source, and external interrupt filtering clock source.

- XTAL: External crystal oscillator, TIM/PWM module clock source.

- SCL: The highest 1MHz clock is used as the IIC slave communication clock source.

- SPI CLK: The highest 4MHz clock is used as the slave SPI communication clock source.

- PGC: The clock within 5M is used as the FLASH programming clock source.

- **SWCLK:** Clock within 20M is used as the clock source for DEBUG and FLASH programming.

Datasheet Page 25 of449

Figure 3.1 Clock block diagram

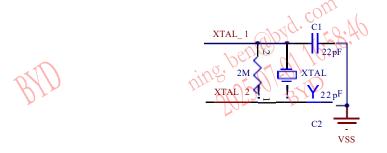

Figure 3.2 External passive crystal oscillator circuit reference

#### Note:

- 1. The external passive crystal oscillator circuit is for reference only, the actual parameters refer to the crystal oscillator specifications;

- 2. The excitation power of external passive 32768Hz crystal oscillator is recommended to be greater than  $1\mu W$ ;

- 3. The external passive 32768Hz crystal oscillator is recommended to have a parallel resistance of  $2M\Omega$ ;

- 4. The external passive 4M/8M crystal oscillator is recommended to have a parallel resistance of  $1M\Omega$ ;

Datasheet Page 26 of449

### 3.2. Registers

Base address: 0x5000 0000

| Address offset                                                                                | Register     | Description                                                               |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------|--|--|--|--|--|

| 0x00                                                                                          | CLK_CFG      | Clock configuration register                                              |  |  |  |  |  |

| 0x04                                                                                          | RCU_EN       | Peripheral module clock control register                                  |  |  |  |  |  |

| 0x08                                                                                          | RST_STATE    | Reset flag register                                                       |  |  |  |  |  |

| 0x0C                                                                                          | XTAL_HS_SEL  | Hysteresis voltage selection of comparator in crystal oscillator register |  |  |  |  |  |

| 0x10                                                                                          | ANA_CFG      | Analog module switch register                                             |  |  |  |  |  |

| 0x14                                                                                          | BOR_CFG      | BOR configuration register                                                |  |  |  |  |  |

| 0x18                                                                                          | WAKE_CFG     | System wake-up configuration register                                     |  |  |  |  |  |

| 0x1C                                                                                          | LVDT_CTRL    | LVDT control register                                                     |  |  |  |  |  |

| 0x20                                                                                          | LVDT_STATE   | LVDT status register                                                      |  |  |  |  |  |

| 0x2C                                                                                          | COM_IO_SEL   | COM port selection configuration register                                 |  |  |  |  |  |

| 0x34                                                                                          | ODRAIN_EN    | Open drain output enable register                                         |  |  |  |  |  |

| 0x38                                                                                          | IIC_IO_CTRL  | IIC control register                                                      |  |  |  |  |  |

| 0x40                                                                                          | RCU_RSTEN    | Peripheral module reset enable register                                   |  |  |  |  |  |

| 0x44                                                                                          | TIM_CLK_SEL  | TIM clock selection register                                              |  |  |  |  |  |

| 0x48                                                                                          | CLK_SEL_RDY  | Clock switch completion flag register                                     |  |  |  |  |  |

| 0x4C                                                                                          | PWM_CLK_SEL  | PWM clock selection register                                              |  |  |  |  |  |

| 0x50                                                                                          | HSPEED EN    | SPI high-speed mode enable register                                       |  |  |  |  |  |

| 0x54                                                                                          | ADC TRIG SEL | ADC hardware trigger source selection register                            |  |  |  |  |  |

| 3.2.1. Clock registers  3.2.1.1. Clock configuration register (CLK_CFG)  Address offset: 0x00 |              |                                                                           |  |  |  |  |  |

| Address offset: (                                                                             | )v()()       | Mrs                                                                       |  |  |  |  |  |

| Address offset.                                                                               |              |                                                                           |  |  |  |  |  |

# 3.2.1. Clock registers

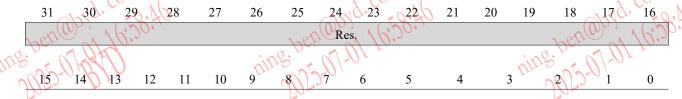

#### 3.2.1.1. Clock configuration register (CLK\_CFG)

Reset value: 0x0000 0002

|    |    | 012000 | 0 000. | _  |    |    |     |     |    |    |    |    |    |      |     |

|----|----|--------|--------|----|----|----|-----|-----|----|----|----|----|----|------|-----|

| 31 | 30 | 29     | 28     | 27 | 26 | 25 | 24  | 23  | 22 | 21 | 20 | 19 | 18 | 17   | 16  |

|    |    |        |        |    |    |    | R   | es. |    |    |    |    |    |      |     |

|    |    |        |        |    |    |    |     |     |    |    |    |    |    |      |     |

| 15 | 14 | 13     | 12     | 11 | 10 | 9  | 8   | 7   | 6  | 5  | 4  | 3  | 2  | 1    | 0   |

|    |    |        |        |    |    | Re | es. |     |    |    |    |    |    | HCLK | SEL |

|    |    |        |        |    |    |    |     |     |    |    |    |    |    | R    | W   |

|   | 4 com        | 4 contr                                          |

|---|--------------|--------------------------------------------------|

|   | 31:2         | Reserved                                         |

| 7 | Den Den      | HCLK clock frequency division selection register |

| 9 | 1:0 HCLK_SEL | 00: 48MHz 01: 32MHz                              |

|   | N F          | 10: 24MHz 11: 12MHz                              |

Page 27 of449 Datasheet

#### 3.2.1.2. Peripheral module clock control register (RCU\_EN)

Address offset: 0x04 Reset value: 0x0000 0001

| 31 | 30 | 29   | 28 | 27    | 26     | 25     | 24     | 23     | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

|----|----|------|----|-------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

|    | R  | les. |    | DIV_  | GPIOD_ | GPIOC_ | GPIOB_ | GPIOA_ | DMA_  | CRC_  | ADC_  | WDT_  | TIM7_ | TIM6_ | TIM5_ |

|    | •  |      |    | CLKEN | CLKEN  | CLKEN  | CLKEN  | CLKEN  | CLKEN | CLKEN | CLKEN | CLKEN | CLKEN | CLKEN | CLKEN |

|    |    |      |    | RW    | RW     | RW     | RW     | RW     | RW    | RW    | RW    | RW    | RW    | RW    | RW    |

| 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | 7      | 6      | 5      | 4      | 3      | 2     | 1     | 0       |

|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-------|-------|---------|

| TIM4_ | TIM3_ | TIM2_ | TIM1_ | TIM0_ | PWM1_ | PWM0_ | IIC_  | UART4_ | UART3_ | UART2_ | UART1_ | UART0_ | SPI1_ | SPI0_ | Res.    |

| CLKEN  | CLKEN  | CLKEN  | CLKEN  | CLKEN  | CLKEN | CLKEN | l ttos. |

| RW     | RW     | RW     | RW     | RW     | RW    | RW    | 200     |

| 31:28 | _           | Reserved                                                                 |

|-------|-------------|--------------------------------------------------------------------------|

|       |             | Reserved  DIV module operation enable  1: Work  0: Off, the default is 0 |

| 27    | DIV_CLKEN   | 1: Work                                                                  |

|       | _           | 0: Off, the default is 0                                                 |

|       |             | GPIOD module operation enable                                            |

| 26    | GPIOD_CLKEN | 1: Work                                                                  |

|       |             | 0: Off, the default is 0                                                 |

|       |             | GPIOC module operation enable                                            |

| 25    | GPIOC_CLKEN | 1: Work,                                                                 |

|       |             | 0: Off, the default is 0                                                 |

|       |             | GPIOB module operation enable                                            |

| 24    | GPIOB_CLKEN | 1: Work                                                                  |

|       |             | 0: Off, the default is 0                                                 |

|       |             | GPIOA module operation enable                                            |

| 23    | GPIOA_CLKEN | 1: Work                                                                  |

|       | PIR         | 0: Off, the default is 0                                                 |